# EVOLUTIONARY ALGORITHMS FOR SYNTHESIS AND OPTIMIZATION OF SQUENTIAL LOGIC CIRCUITS

Ву

Belgasem Ali

BSc, MSc, MIEE

A thesis submitted in partial fulfilment of the requirements for the degree of

**Doctor of Philosophy**

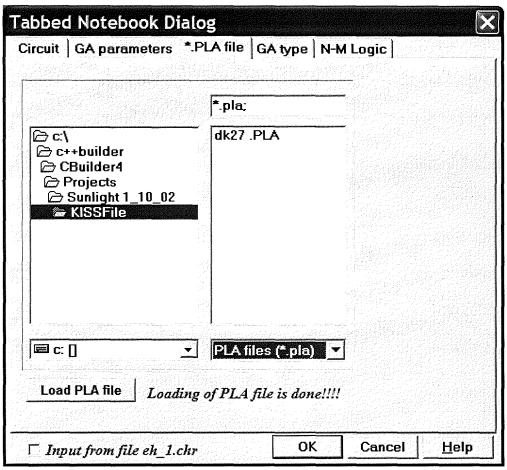

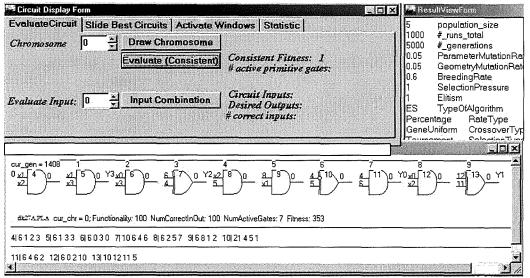

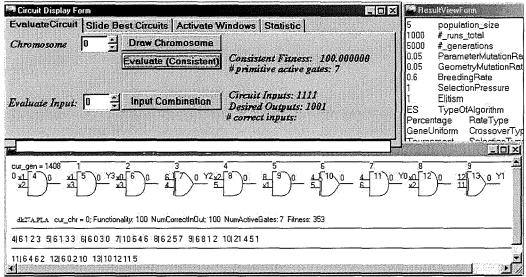

Napier University

Edinburgh

May 2003

© Copyright by Belgasem Ali

#### **Abstract**

Considerable progress has been made recently in the understanding of combinational logic optimization. Consequently a large number of university and industrial Electric Computing Aided Design (ECAD) programs are now available for optimal logic synthesis of combinational circuits. The progress with sequential logic synthesis and optimization, on the other hand, is considerably less mature.

In recent years, evolutionary algorithms have been found to be remarkably effective way of using computers for solving difficult problems. This thesis is, in large part, a concentrated effort to apply this philosophy to the synthesis and optimization of sequential circuits.

A state assignment based on the use of a Genetic Algorithm (GA) for the optimal synthesis of sequential circuits is presented. The state assignment determines the structure of the sequential circuit realizing the state machine and therefore its area and performances. The synthesis based on the GA approach produced designs with the smallest area to date. Test results on standard finite state machine (FSM) benchmarks show that the GA could generate state assignments, which required on average 15.44% fewer gates and 13.47% fewer literals compared with alternative techniques.

Hardware evolution is performed through a succession of changes/reconfigurations of elementary components, inter-connectivity and selection of the fittest configurations until the target functionality is reached.

The thesis presents new approaches, which combine both genetic algorithm for state assignment and extrinsic Evolvable Hardware (EHW) to design sequential logic circuits. The implemented evolutionary algorithms are able to design logic circuits with size and complexity, which have not been demonstrated in published work.

There are still plenty of opportunities to develop this new line of research for the synthesis, optimization and test of novel digital, analogue and mixed circuits. This should lead to a new generation of Electronic Design Automation tools.

#### **ACKNOWLEDGEMENTS**

I would like to thank my supervisors Prof. A.E.A Almaini, Mr. M. MacCallum (Napier University) and Dr. T Kalganova, (University of Brunel), for their guidance, help, and constant support. I very much appreciate their immense patience and willingness to discuss my ideas about evolution, adaptation, electronic circuits design, and of course, science. I am grateful to Prof. T Muneer for always leaving his door open for stimulating discussions on science and many other problems that may occur in the world of Human beings. I am grateful to members our research group, and especially to Dr. Y. Xia, Dr. L. Wang, K. Farag and M. Yang for being colleague and a good friends.

Thanks also to those people who contributed anonymously by reviewing different parts of the thesis that later on have appeared as publications in journals and conference proceedings.

Finally, I would like to thank my parents for being patient with me, my brothers for their support, and my wife, for being always on my side in the struggle for survival.

I would like to say to those people that I am indebted to them for life and that the memories of the time spent with them at Napier University will always be with me, cherished forever and relived again and again.

#### **DECLARATION**

I hereby declare that I have carried out all the work presented in this thesis. No part of this work has previously been submitted in support of a degree validated by this or any other University.

B. Ali Supull Mariell

#### TABLE OF CONTENTS

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VIII                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | XI                         |

| List of Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XIII                       |

| Chapter 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

| General Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| 1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14791011                   |

| 2.1 Introduction 2.2 Overview of optimal logic synthesis 2.3 Logic synthesis with ECAD tools 2.4 VLSI Design Flow 2.5 Probing the limits of Logic Synthesis 2.6 Sequential logic synthesis 2.6.1 Sequential circuits 2.6.2 Early work on sequential logic synthesis 2.6.3 Classic Synthesis Trajectory 2.6.3.1 State Minimization 2.6.3.2 State assignment of finite state machines 2.6.3.3 A Problem with existing state assignment approaches 2.6.4 Concurrent state minimization and assignment to improve area. | 16 18 23 25 25 29 30 31 32 |

| 2.7 CAD Algorithms and tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| 2.8 Other approaches to FSM design and optimaztion.               |          |

|-------------------------------------------------------------------|----------|

| Chapter 3                                                         |          |

| Evolutionary Algorithms: A tool for Digital design                |          |

| 3.1 Introduction                                                  | 42       |

| 3.2 Outline of Evolutionary Algorithms                            | 43       |

| 3.2.1 Genetic Algorithms                                          | 45       |

| 3.2.1.1 Usage Requirements of Genetic Algorithms                  |          |

| 3.2.1.2 Genetic Operators                                         | 52       |

| 3.2.1.3 Elitist Selection and Fitness Scaling                     |          |

| 3.2.2 Genetic Programming                                         |          |

| 3.2.2.1 GP Crossover Operator                                     | 56       |

| 3.2.2.2 GP Mutation                                               | 57       |

| 3.2.3 Evolutionary Programming                                    | 57       |

| 3.2.4 Evolution Strategies                                        |          |

| 3.2.5 Phenotypic versus Genotype Evolution                        |          |

| 3. 3 Evolutionary designs of digital circuits                     |          |

| 3.4 Evolvable Hardware                                            |          |

| 3.4.1 Introduction                                                |          |

| 3.4.2 Taxonomy of EHW                                             |          |

| 3.4.2.1 Evaluation process                                        | 65       |

| 3.4.2.1.1 Extrinsic EHW                                           |          |

| 3.4.2.1.2 Intrinsic EHW                                           |          |

| 3.4.2.2 Evolving platform                                         |          |

| 3.4.2.3 Evolution process                                         |          |

| 3.5 Differences from traditional methods                          |          |

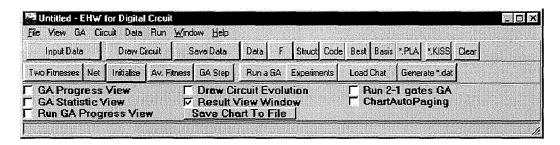

| 3.6. Evolvable hardware implementation                            |          |

| 3.6.1 Advantages of evolutionary design                           |          |

| 3.6.2 Disadvantage of evolutionary design                         |          |

| 3.7 Summary                                                       | 77       |

| Chapter 4                                                         |          |

| Optimal State Assignment of Finite State Machine                  |          |

| 4.1 Introduction                                                  | 70       |

|                                                                   |          |

| 4.2 Complexity of the state assignment problem                    | /ソ<br>Q1 |

|                                                                   |          |

| 4.2.2 Motivation example                                          |          |

| 4.4 Mechanical state assignment                                   |          |

| 4.5 Previous Application of Genetic Algorithm to State Assignment |          |

| 4.6 Genetic Algorithms for states assignment problem              |          |

| no Centere ingominis for states assignment problem                |          |

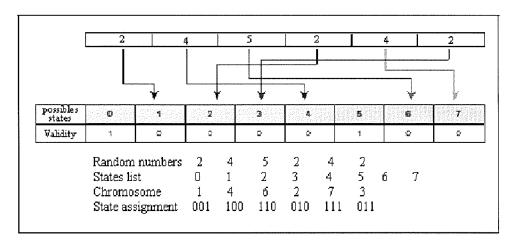

| 4.6.1 Chromosome representation for GA State assignment problem  | 90  |

|------------------------------------------------------------------|-----|

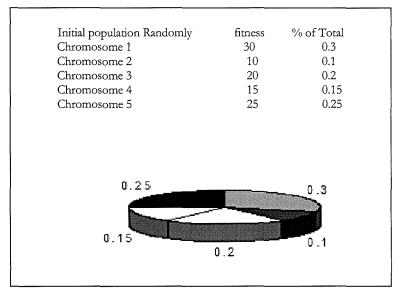

| 4.6.2 Fitness function                                           | 92  |

| 4.7 Genetic operators                                            | 94  |

| 4.8 Experimental results                                         |     |

| 4.8.1 Parameter Effects                                          | 98  |

| 4.8.2 Parameter space                                            |     |

| 4.8.3 Crossover and mutation                                     | 100 |

| 4.8.4 Population Size                                            | 105 |

| 4.8.5 GA Generation                                              | 108 |

| 4.9 Comparison of results                                        |     |

| 4.10 Comparison of GA algorithm with different approaches        |     |

| 4.11 Discussion of Results                                       | 121 |

| 4.12 Summary                                                     | 122 |

|                                                                  |     |

| Chapter 5                                                        |     |

| Evolutionary Design for logic Circuits                           |     |

|                                                                  |     |

| 5.1 Introduction                                                 |     |

| 5.2 The space of all representations                             |     |

| 5.2.1 Representation of Boolean function                         |     |

| 5.2.2 Reed-Muller function                                       |     |

| 5.2.3 Mixed function                                             |     |

| 5.3 Backgrounds and Motivation                                   |     |

| 5.4 Basic idea of the proposed approach                          |     |

| 5.5 Problem Modelling                                            |     |

| 5.6 Encoding of evolution                                        |     |

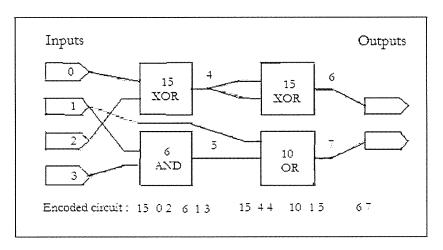

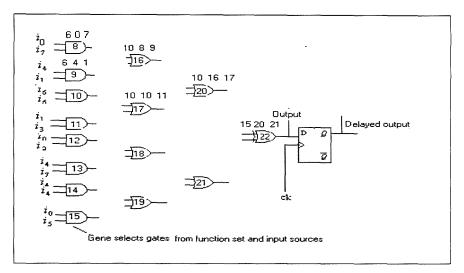

| 5.6.1 Chromosome representation and connectivity                 | 140 |

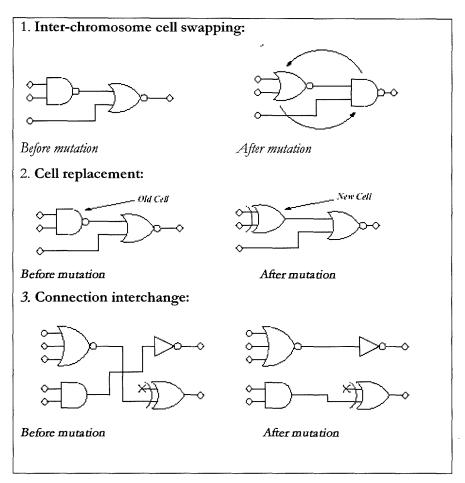

| 5.6.2 Genetic operators                                          |     |

| 5.6.3 Connection repair algorithm                                | 146 |

| 5.6.4 Criteria used in an extrinsic EHW                          | 147 |

| 5.6.4.1 Fitness function                                         | 148 |

| 5.6.4.2 Test vectors                                             |     |

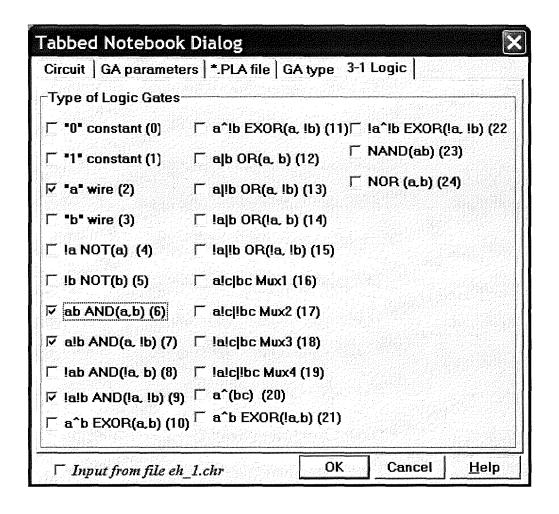

| 5.6.5 Definition of subcircuits for combinational logic circuits | 150 |

| 5.7 Experimental results                                         | 153 |

| 5.7.1 Example 1: Serial Adder                                    |     |

| 5.7.2 Example 2: Module-4 counter                                |     |

| 5.7.3 Example 3: sequence detector                               |     |

| 5.7.4 Example 4: 1010 detector                                   |     |

| 5.8 Analysis of the results                                      |     |

| 5.9 Summary                                                      |     |

|                                                                  |     |

### Chapter 6

### Extrinsic Evolution of Finite State Machine

| 169 |

|-----|

| 169 |

| 172 |

| 173 |

| 181 |

| 186 |

|     |

|     |

| 187 |

| 192 |

| 194 |

| 195 |

|     |

| A-1 |

| B-1 |

|     |

| D-1 |

|     |

# List of figures

| Number                                                                                | Page |

|---------------------------------------------------------------------------------------|------|

| Figure 1.1. Space of all designs                                                      | 9    |

| Figure 2.1. Typical VLSI design flow in three domains (Y-chart representation).       | 20   |

| Figure 2.2. A more simplified view of VLSI design flow                                | 21   |

| Figure 2.3. Level of design                                                           | 23   |

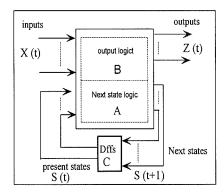

| Figure 2.4. Structure view of a finite state machine.                                 | 26   |

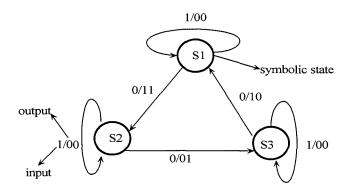

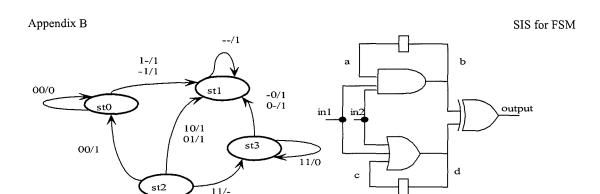

| Figure 2.5. An example of a State Transition Graph (STG)                              | 28   |

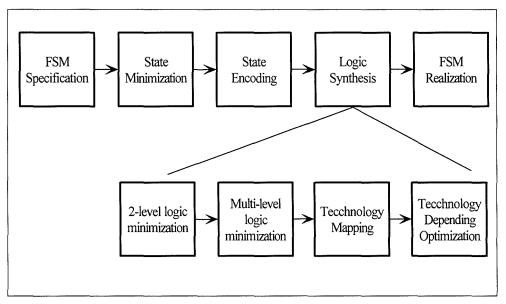

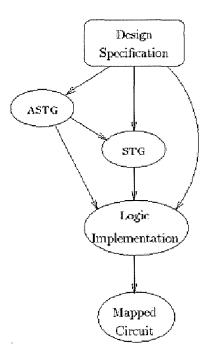

| Figure 2.6. Traditional sequential synthesis trajectories.                            | 31   |

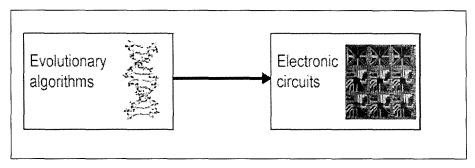

| Figure 3.1. Use of the evolutionary algorithms (EA) to create electronic circuits     | 43   |

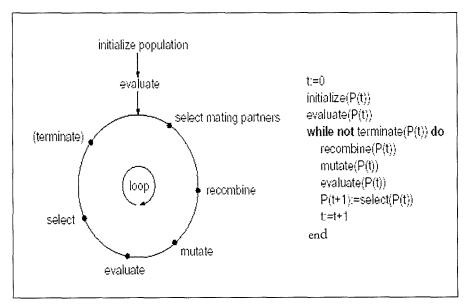

| Figure 3.2. General outlines of any evolutionary algorithms method.                   | 43   |

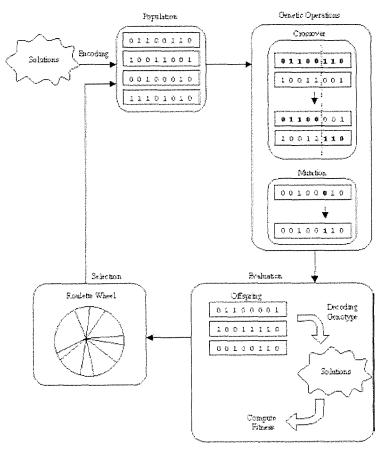

| Figure 3.3. Execution of the genetic algorithms.                                      | 45   |

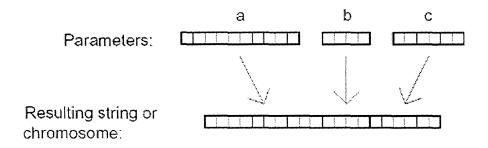

| Figure 3.4. Coding of three parameters in a single string                             | 47   |

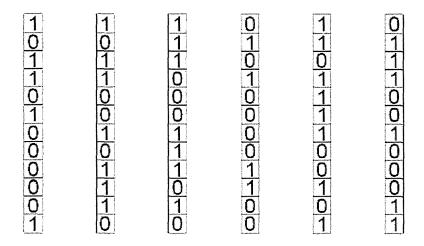

| Figure 3.5.A Random initial population with chromosome length of 12 bits              | 48   |

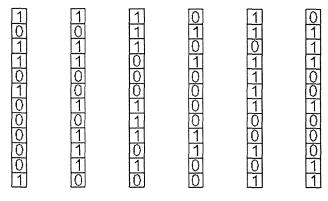

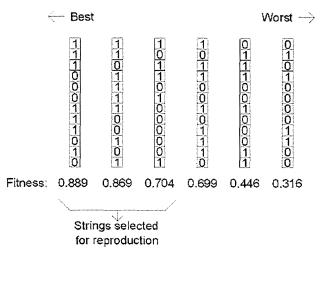

| Figure 3.6. The fitness of each string has been computed.                             | 49   |

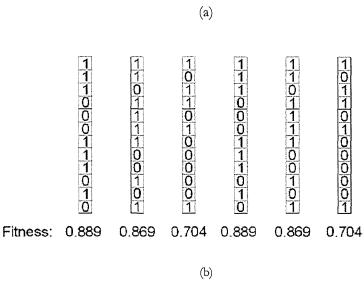

| Figure 3.7. The new population with the rank method                                   | 50   |

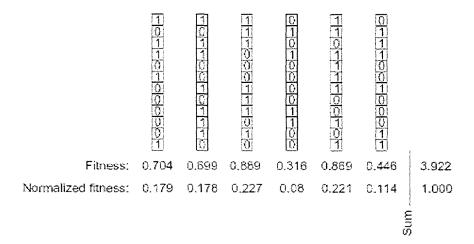

| Figure 3.8. The fitness of the strings is normalized.                                 | 51   |

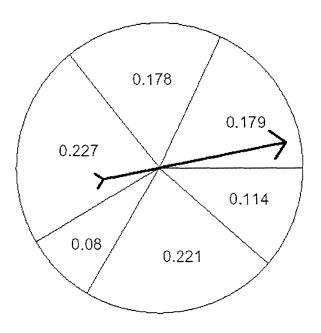

| Figure 3. 9. The biased roulette wheel.                                               | 51   |

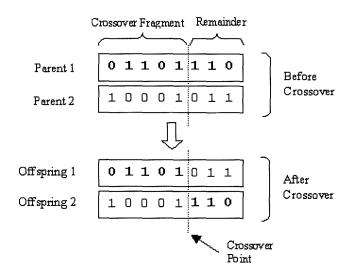

| Figure 3.10. Single point crossover operator.                                         | 53   |

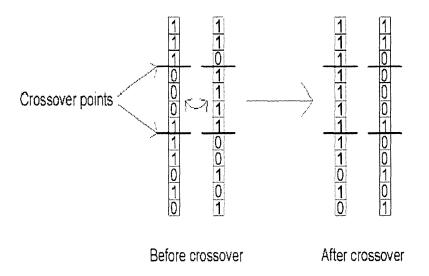

| Figure 3.11. Two point crossover.                                                     | 53   |

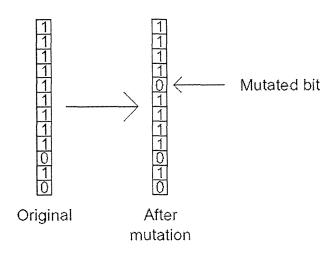

| Figure 3.12. The mutation operator changed a random bit of the string.                | 54   |

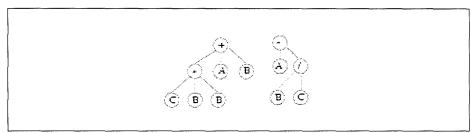

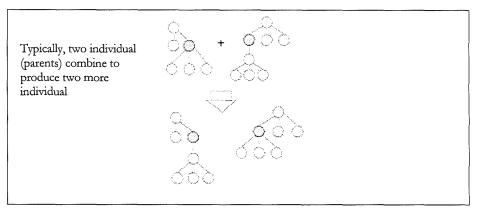

| Figure 3.13. GP example.                                                              | 56   |

| Figure 3.14. Simplified GP crossover operators.                                       | 57   |

| Figure 3.15. Evolutionary programming algorithms.                                     | 58   |

| Figure 3.16. The evolution strategy algorithm.                                        | 59   |

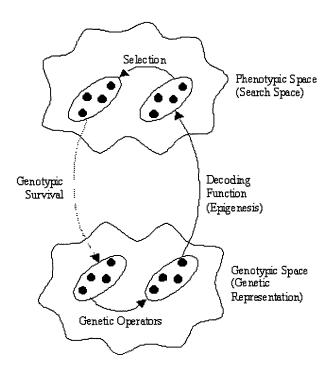

| Figure 3.17. Mapping between genotype space and phenotypic space.                     | 60   |

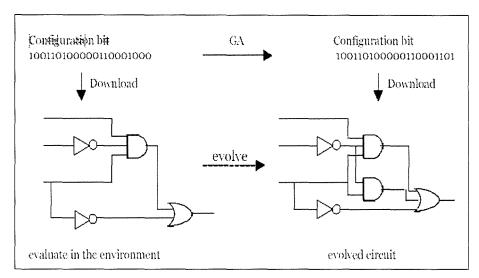

| Figure 3.18. The concept scheme of Evolvable hardware.                                | 63   |

| Figure 3.19. Circuit design problem in EHW. In EHW approach, the circuits in initial  |      |

| population are generated randomly and do not implement the desired logic function.    |      |

| Therefore, an evolutionary algorithm design a circuit that correctly implements given |      |

| logic function and optimises fully functional circuit. In other words, evolutionary           |     |

|-----------------------------------------------------------------------------------------------|-----|

| algorithm evolves a logic circuit [24]                                                        | 64  |

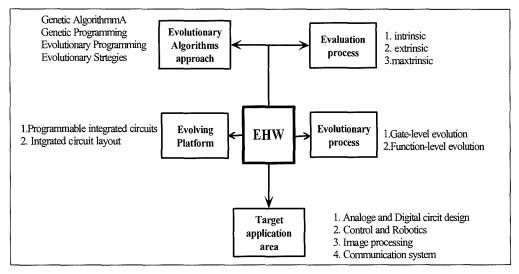

| Figure 3.20. Taxonomy of Evolvable Hardware.                                                  | 65  |

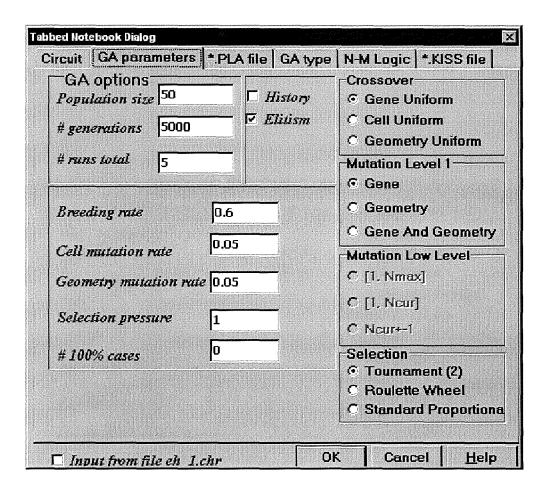

| Figure 3.21. On-line EHW                                                                      | 68  |

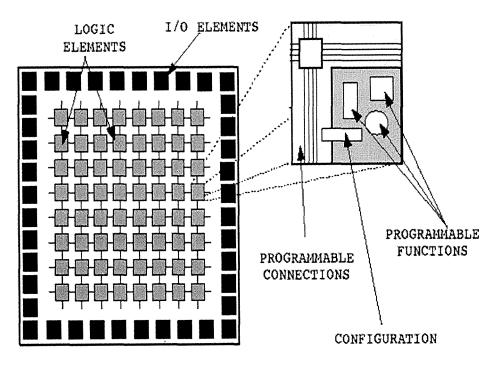

| Figure 3.22. Basic structure of a generic FPGA circuit.                                       | 69  |

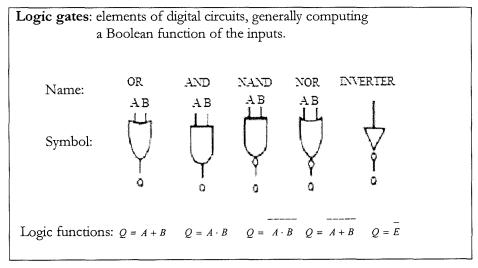

| Figure 3.23. The primitive logic gates.                                                       | 71  |

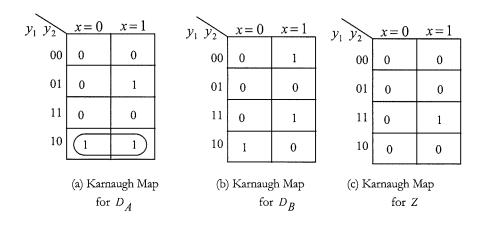

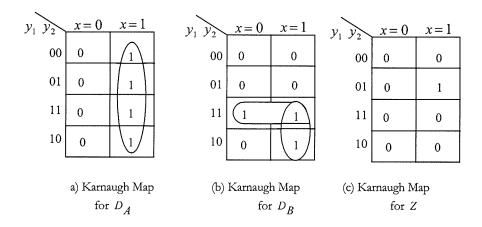

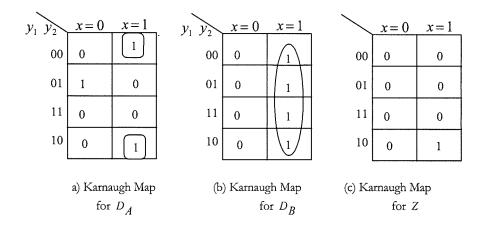

| Figure 4.1. Karnaugh maps for D flip-flops realization and output for assignment 1.           |     |

| Figure 4.2. Karnaugh maps for D flip-flops and output for assignment 2.                       |     |

| Figure 4.3. Karnaugh maps for D flip-flops and output for assignment 3.                       |     |

| Figure 4.5. Roulette wheel parent selection                                                   |     |

| Figure 4.7. Effect of Crossover and mutation on chromosome Fitness                            |     |

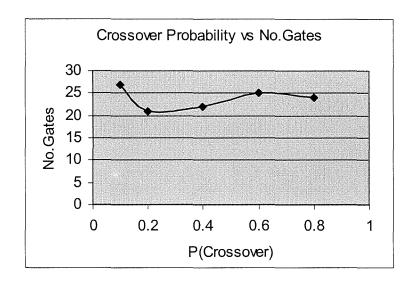

| Figure 4.8 Effect of P (Crossover) for example modulo12                                       |     |

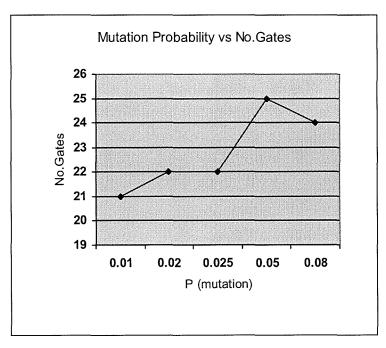

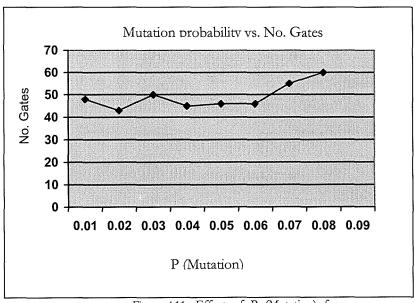

| Figure 4.9. Effect of P (Mutation) for example modulo12                                       |     |

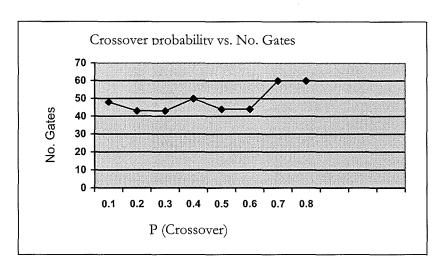

| Figure 4.10. Effect of P (Crossover) for example dk512                                        |     |

| Figure 4.11. Effect of P (Mutation) for example dk512                                         |     |

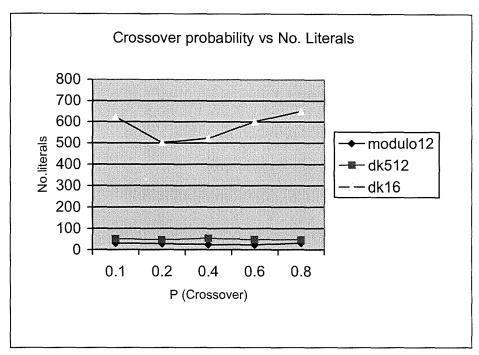

| Figure 4.12. Effect of P (Crossover) for examples modulo12, dk512 and dk16                    |     |

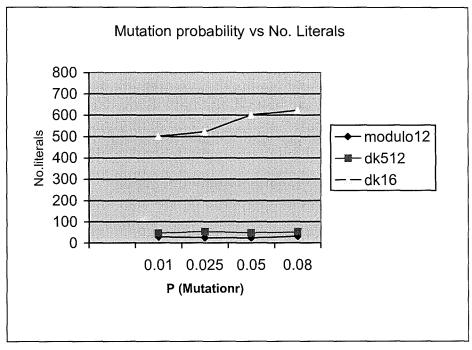

| Figure 4.13. Effect of P (Mutation) for examples modulo12, dk512 and dk16                     |     |

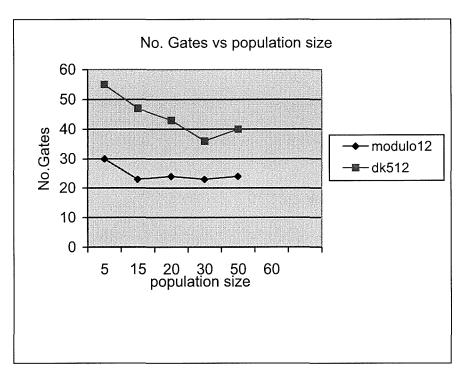

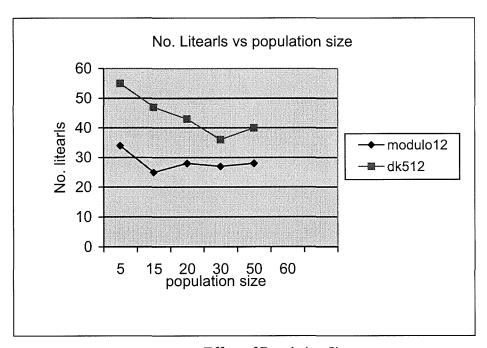

| Figure 4.14. Effect of Population Size.                                                       |     |

| Figure 4.15. Effect of Population Size                                                        | 107 |

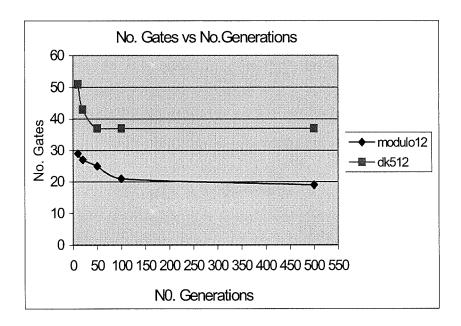

| Figure 4.16. Variation of No. Generations with No. Gates                                      |     |

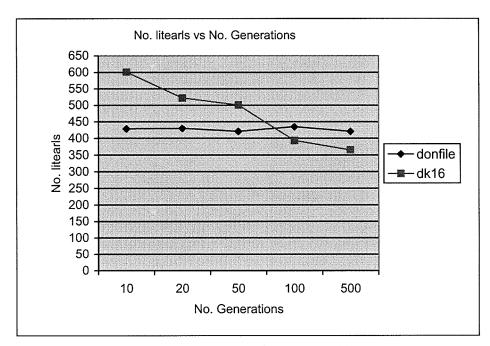

| Figure 4.17. Variation of No. Generations with No. liearls                                    |     |

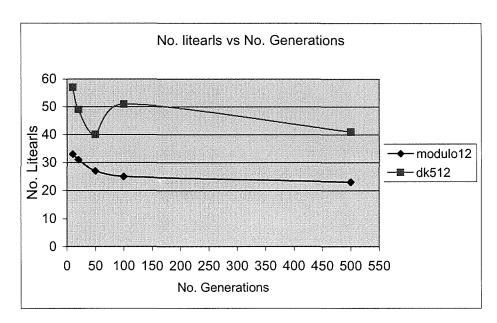

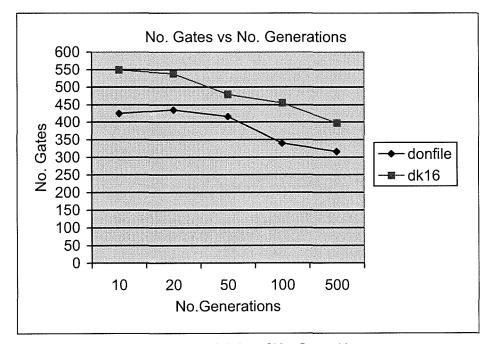

| Figure 4.18. Variation of No. Gates with No. Generations                                      | 110 |

| Figure 4.19. Variation of No. literals with No. Generations                                   | 111 |

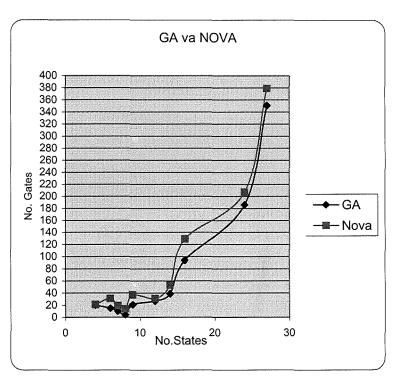

| Figure 4.20. Comparison of GAs with Nova based on number of gates                             | 114 |

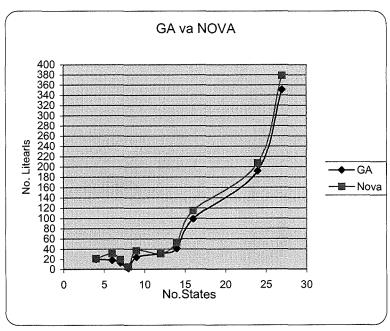

| Figure 4.21. Comparison of GAs with Nova based on number of Literals.                         | 114 |

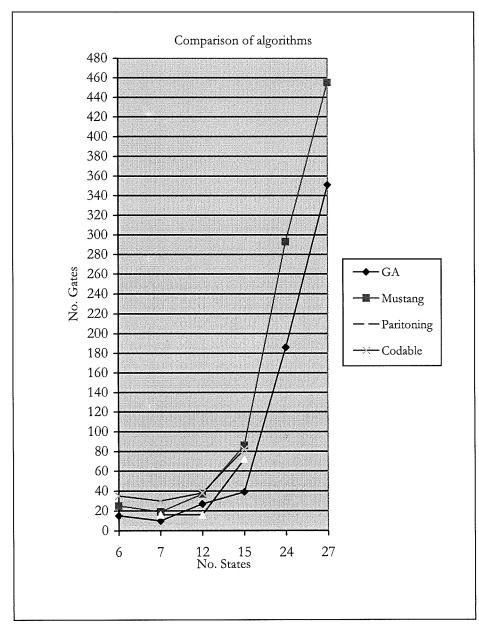

| Figure 4.22. Comparison of GA with Mustang, Partitioning and codable column                   | 119 |

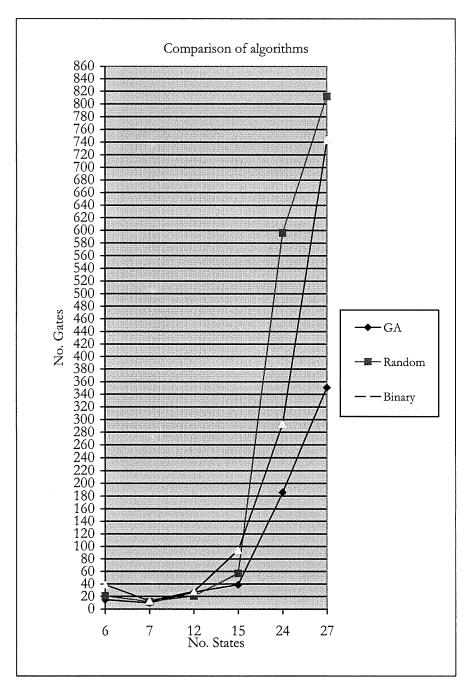

| Figure 4.23. Comparison of GA with Random and binary state assignments                        | 120 |

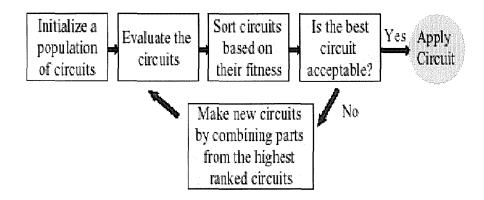

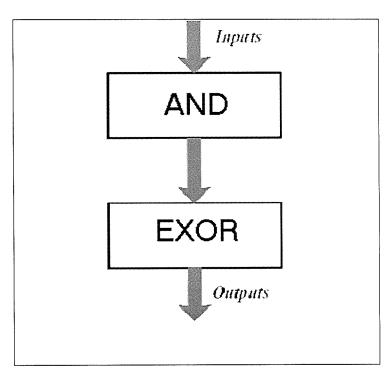

| Figure 5.1. The automatically circuit designed using an adaptive algorithm                    | 124 |

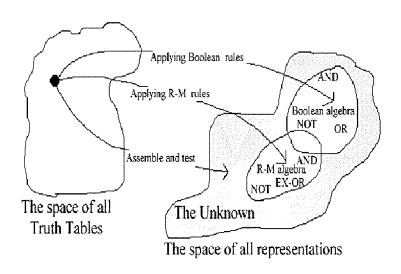

| Figure 5.2. How assemble-and-test reaches the unknown regions of the space of all             |     |

| representations                                                                               | 126 |

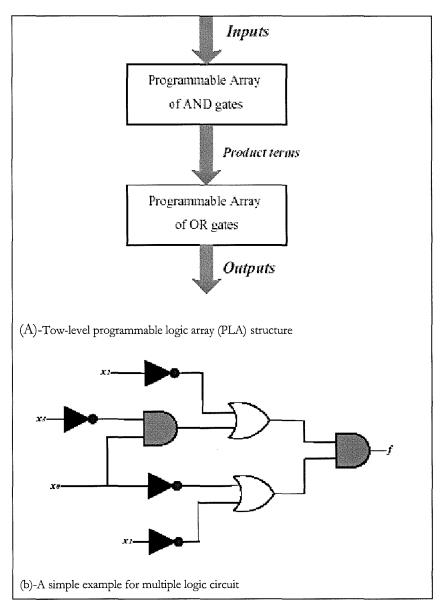

| Figure 5.3. Comparison between two-level and multilevel structures                            | 128 |

| Figure 5.4. RM form is an exclusive-OR sum of products                                        | 129 |

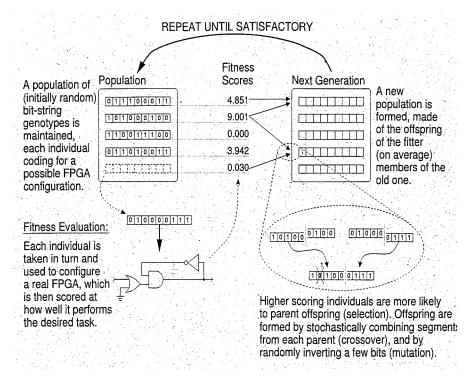

| Figure 5.5. Evolving an FPGA configuration using a simple genetic algorithm                   | 132 |

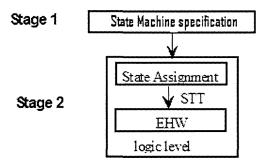

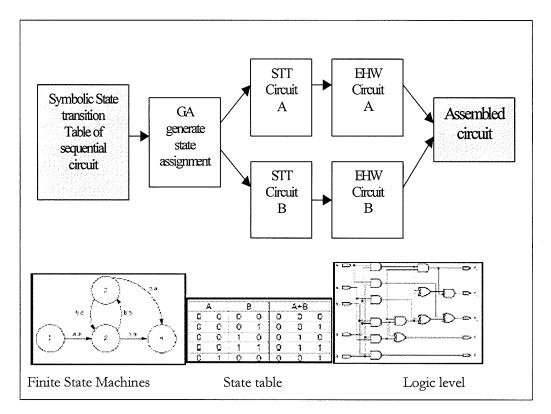

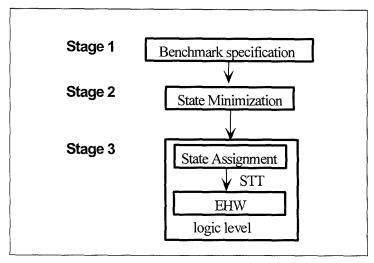

| Figure 5.6. Procedure of the proposed approach to design sequential logic circuit using       |     |

| genetic algorithm and extrinsic evolvable hardware                                            |     |

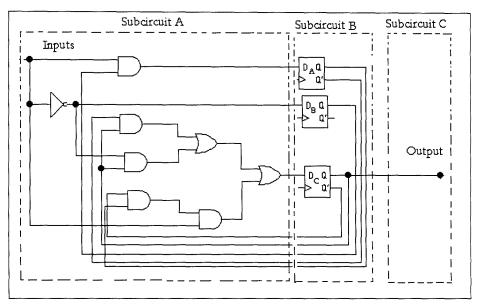

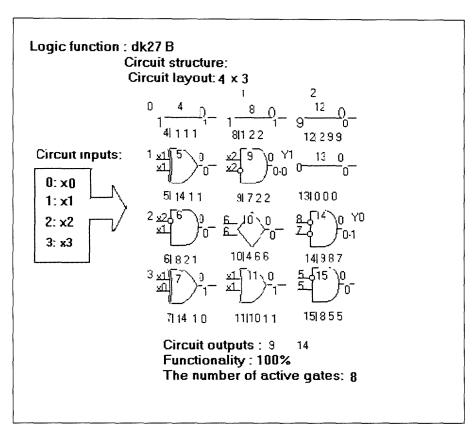

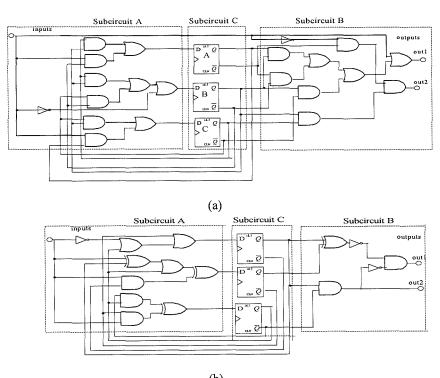

| Figure 5.7. Description of the circuit's parts                                                | 138 |

| Figure 5.8. The procedure of generating the circuits from the symbolic state transition table | 139 |

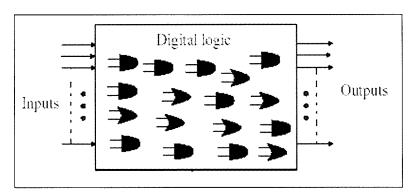

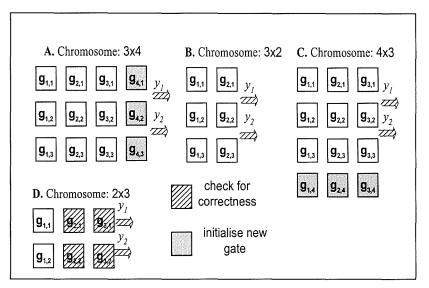

| Figure 5.9. The representations for a hypothetical inputs/outputs                                 | 140 |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 5.10 Schematic of the chromosome structure used in EHW approach with layout 2x2            | 141 |

| Figure 5.11. Three mutation operators used by the genetic algorithm.                              |     |

| Figure 5.12. The geometry mutation process (3x3 circuit geometry) [24]                            | 145 |

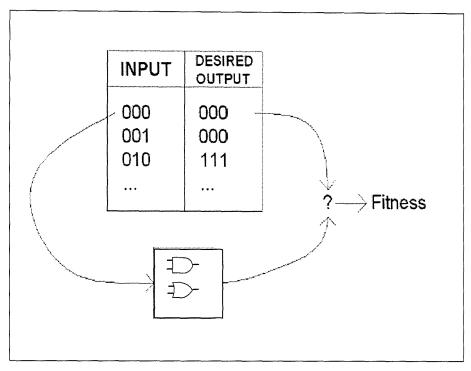

| Figure 5.13. Test vectors.                                                                        | 150 |

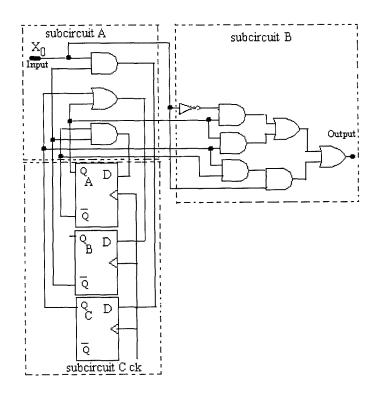

| Figure 5.14. Circuit structure is implemented according to state table given in Table 5. 3        | 152 |

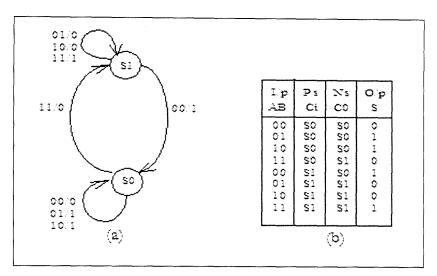

| Figure 5.15. Serial adder (a) State transition graph, and (b) state transition table ; where #I/p |     |

| inputs, #Ps present state, #Ns Next state, #O/p Outputs                                           | 155 |

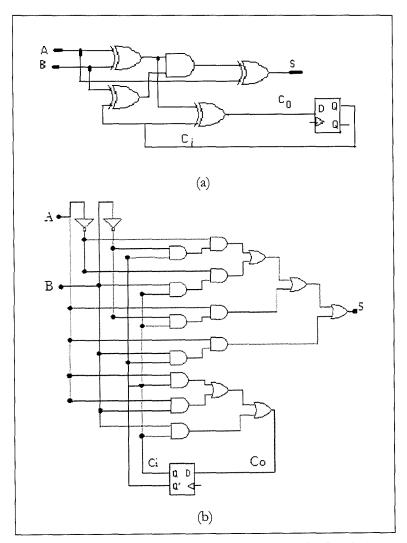

| Figure 5.16. Evolved Serial adder using (a) functional set (0-6, 15,16), (b) functional set (0-6, |     |

| 10)                                                                                               | 156 |

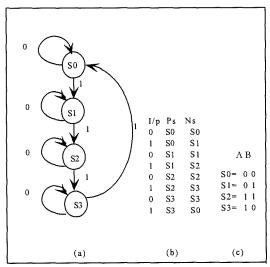

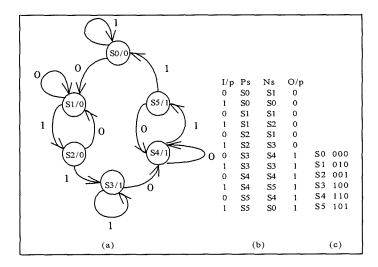

| Figure 5.17. Module-4 counter a)-state transition graph, b) State table and c) State assignment   |     |

| generated by GA                                                                                   | 157 |

| Figure 5.18. Evolved optimal circuit solution of the model-4 counter                              | 158 |

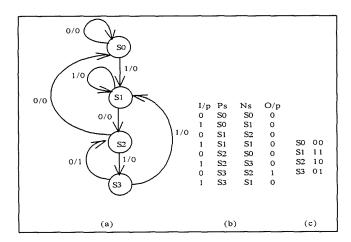

| Figure 5.19. A sequence detector described as a) state transition graph, b) state table, c) State |     |

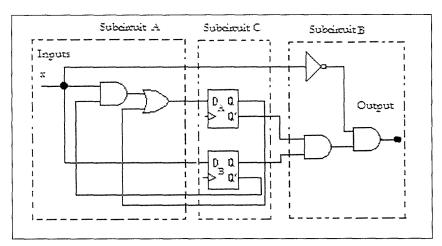

| assignment generated by GA                                                                        | 159 |

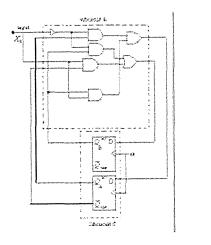

| Figure 5.20. Evolved optimal circuit solution of the sequence detector with circuit layout 4x5    | 161 |

| Figure 5.21. 1010 Detector a) state transition graph, b) state transition table, c) state         |     |

| assignment                                                                                        | 161 |

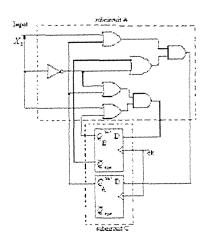

| Figure 5.22. Evolved optimal circuit solution for 1010 detector using 4x5-circuit layout          | 162 |

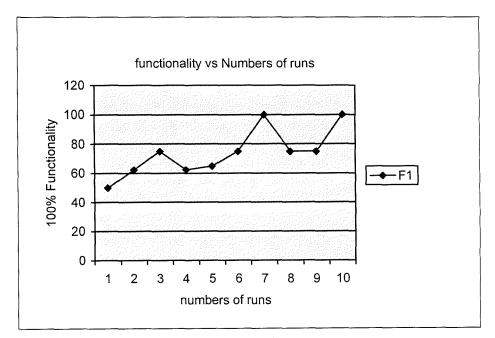

| Figure 5.23. Fitness distribution in 10 runs                                                      | 165 |

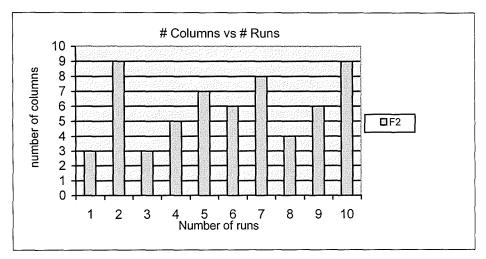

| Figure 5.24.The graphic illustration how the circuit layout and evolves functionality affect the  |     |

| solutions of sequence detector.                                                                   | 166 |

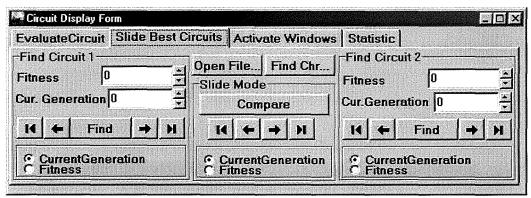

| Figure 6.1. Procedure of the proposed approach to design FSM circuit using genetic algorithm      |     |

| and extrinsic evolvable hardware                                                                  | 170 |

| Figure 6.2. Gate level representation of a sequential circuit.                                    | 171 |

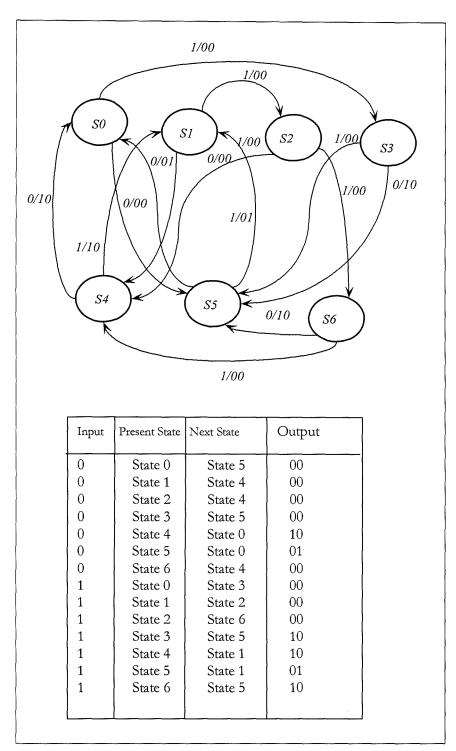

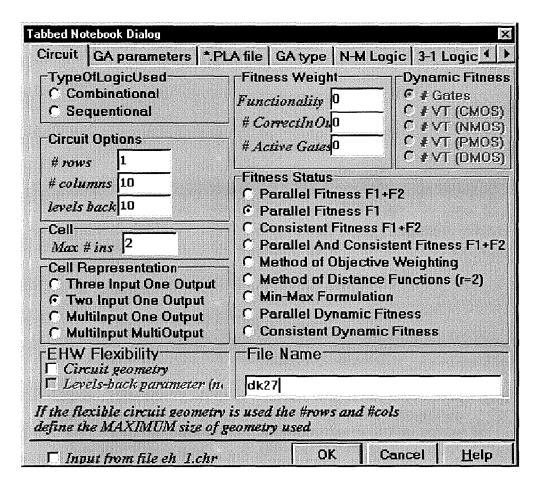

| Figure 6.3. DK27 State Diagram and symbolic state transition table                                | 175 |

| Figure 6.4.The procedure of generation the *.pla file from the state transition table based on    |     |

| example of dk27 (Kiss2 benchmark). Step1 shows the initial symbolic State                         |     |

| Transition Table, Step2 generates State Assignments using the genetic algorithm and               |     |

| Step 3 generates the PLA files (*.pla) based on the state assignments obtained                    | 176 |

| Figure 6.5. An example of the phenotype and corresponding genotype of a chromosome with           |     |

| 3x4 circuit layout. Functional set (0-15).                                                        | 178 |

| Figure 6.6. An example of the phenotype and corresponding genotype of a chromosome with           |     |

| 3x4 circuit layout. Functional set (0-15)                                                         | 179 |

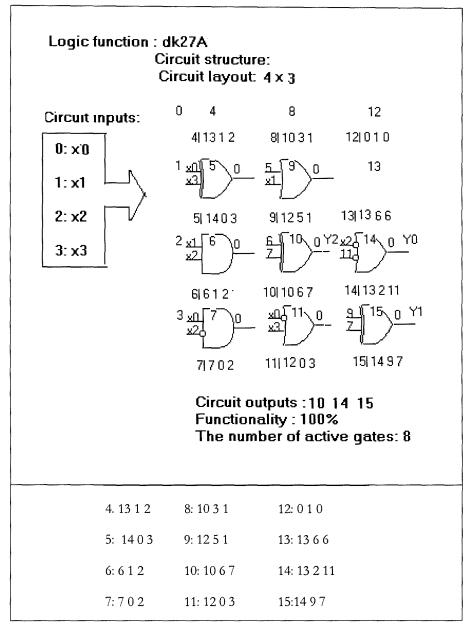

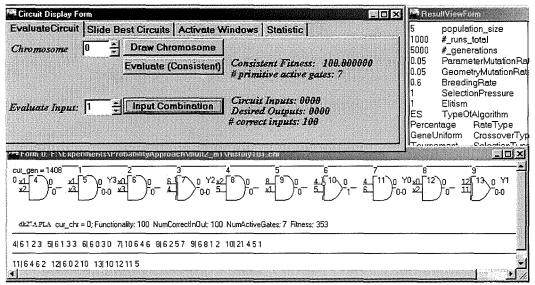

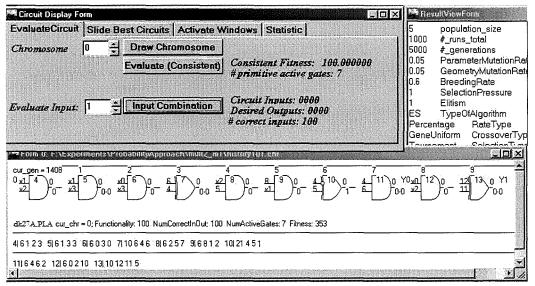

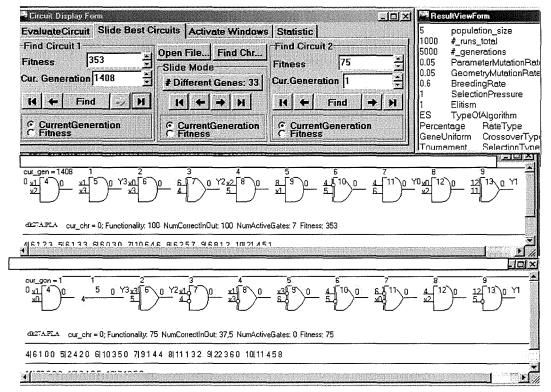

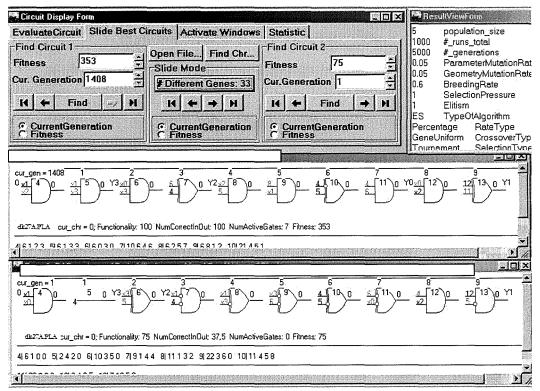

| Figure 6.7. Evolved dk27 design using (a) functional set (0-10) (b) functional set (0-15)         | 180 |

#### LIST OF TABLES

| Number                                                                                     | Page |

|--------------------------------------------------------------------------------------------|------|

| Table 1.1 Some key publication in evolutionary electronics                                 | 6    |

| Table 2.1. An example of a State Transition Table (STT)                                    |      |

| Table 2.2. Some Commercial design Synthesis tools.                                         |      |

| Table 3.1. Paradigms in Evolutionary Algorithms                                            |      |

| Table 3.2. The different between design process and Evolution process.                     |      |

| Table 4.1. Number of Different state assignments.                                          |      |

| Table 4.2. State Table with three State Assignments                                        |      |

| Table 4.3. State transition t able for assignment 1.                                       |      |

| Table 4.4. State transition table for assignment 2.                                        |      |

| Table 4.5. State transition table for assignment 3.                                        |      |

| Table 4.6. Gate comparison for three state assignments                                     |      |

| Table 4.7. Summary of available approaches to find optimal state assignment                |      |

| Table 4.8. Example state mutation                                                          |      |

| Table 4.9. Statistics of benchmark examples                                                |      |

| Table 4.10. Compression crossover and mutation.                                            |      |

| Table 4.11. Population size numbers of gates and number of literal                         |      |

| Table 4.12. Result number of generation                                                    | 109  |

| Table 4.13. Comparison of GAs with Nova based on the number of gates.                      | 113  |

| Table 4.14. Comparison of GA with Nova based on the number of literal                      | 115  |

| Table 4.15. Results for some Benchmark circuits                                            | 117  |

| Table 4.16. State assignments for each algorithm.                                          | 117  |

| Table 4.17. Comparison of GA state assignment with optimal algorithms.                     | 118  |

| Table 4.18. Comparison of GAs state assignment with mechanical algorithms.                 | 118  |

| Table 5.1. Recent EHW approach used to evolve sequential logic circuits                    | 135  |

| Table 5.2. The full set of components, gates 0 to 15 and their logic functions.            | 142  |

| Table 5.3. The transformation process of STT in to PLA file format. Where i inputs = input |      |

| + present state bits, .o designed the number of outputs calculated, outputs =next          |      |

| state +output bits, .p is the number of product terms, .e is end of file                   | 151  |

| Table 5.4. Initial parameters used to evolve a circuit.                                    | 152  |

| Table 5.5. Solution obtained for serial adder using EHW approach and manual method [1]     | 155  |

| Table 5.6. Solution obtained for model 4 counter using FHW approach and manual method      | 150  |

| Table 5.7. Solutions obtained for sequential detector produced by proposed approach and  |     |

|------------------------------------------------------------------------------------------|-----|

| manual method                                                                            | 160 |

| Table 5.8. Solution obtained for 1010 detector produced using proposed method and manual |     |

| design.                                                                                  | 162 |

| Table 5.9. Initial parameters used to evolve the circuits and their results.             | 164 |

| Table 5.10. Sequence detector experimental results the algorithm performance during the  |     |

| circuit layout and functionality distributions with variable circuit structure and       |     |

| Function set: 2,6,7,8                                                                    | 165 |

| Table 5.11. Module-4 counters with fixed circuit geometry and Function set: 2-8,12.      | 167 |

| Table 6.1. Initial parameter used to evolve sequential logic circuit (Dk27.kiss2)        | 174 |

| Table 6.2. A typical netlist chromosome for 100% functional of Dk27A next state logic    | 179 |

| Table 6.3. State assignments generated by GA.                                            | 181 |

| Table 6.4. Experimental results of extrinsic EHW approach.                               | 183 |

| Table 6.5. Experimental results of extrinsic EHW approach. #in, #out and #stat are the   |     |

| number of inputs, outputs and states respectively. #100 cases is the number of fully     |     |

| functional solutions obtained after 100 runs of GA. The evolved circuits which are       |     |

| more optimal in comparison with SIS [73] are shown in bold                               | 185 |

#### **GLOSSARY**

#### List of Abbreviations

AI Artificial Intelligent

ALU Arithmetic Logic Unit

ASIC Application Specific Integrated Circuit

ASM Algorithm State Machine

BDD Binary Decision Diagram

BDT Binary Decision Tree

BE Boolean Expression

BED Binary Expression Diagram

CAD Computer Aided Design

CMOS Complementary Metal-Oxide-Semiconductor

CNF Conjunctive Normal Form

CPU Central Processing. Unit

CSP Constraint Satisfaction Problems

DNA Deoxyribo Nucleic Acid

DNF Disjunctive Normal Form

DSP Digital Signal Processing

EA Evolutionary Algorithms

EECD Evolutionary Electronic Circuit Design

EHW Evolvable Hardware

EP Evolutionary Programming

ES Evolutionary Strategy

ECAD Electronic Computer Aided Design

FPGA Field Programmable Gate Array

FSM Finite State Machine

FBDD Functional Binary Decision Diagram

GAL Generic Array Logic

GAs Genetic Algorithms

GP Genetic Programming

HDL Hardware Description Language

ICs Integrated Circuits

ITE If\_Then\_Else normal form

KISS Keep Internal State Simple

LSI Large Scale Integration

LUT Look-Up Table

MOS Metal oxide semiconductor

MCNC Microelectronic Centre of North Carolina

NP class of Non-Deterministic

OX Output Circuit Crossover

OFDD Ordered Functional Decision Diagram

PALs Programmable Array Logic

PBIL Population Based Incremental Learning

PLD Progranatnable Logic Device

PLA Programmble logic Array

POS Product Of Sums normal form

R-M Reed-Muller

ROM Read Only Memory

ROBDD Reduced Ordered Binary Decision Diagram

RDAG Rooted and Directed Acyclic Graph

RTL Register transfer level

SA Simulated Annealing

SIS Sequential Interactive System

SOC System On Chip

SOP Sum Of Products

SPICE Simulation Program with Integrated Circuit Emphasis

STG State Transition Graph

STT State Transition Table

TT Truth Table

TSP Travelling Salesman Problem

ULM Universal Logic Module

VGA Variable Length Chromosome

VLSI Very Large Scale Integration

XOR Exclusive OR

#### TERMINOLOGY USED IN THE THESIS

Logic design: A design as a network of logical components

**Logic synthesis:** A usual way of carrying out logic design in which gates are generation from an abstract behavioural/structure description.

**Netlist:** A complete structural description of a circuit, which is ready to implement.

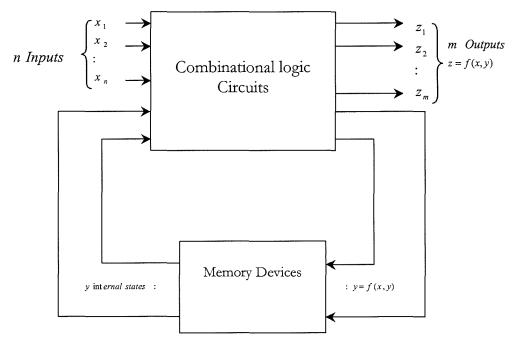

#### Combinational circuit:

A circuit is combinational if it computes a function, which depended only on the inputs applied to the circuit; for every input value, there is a unique output value.

#### Sequential circuit

Sequential circuits are basically combinational circuits with additional storage elements and feedback.

*State minimization*: Combine equivalent states of a state machine to reduce the number of states. For most cases, minimizing the states results in smaller logic, although this is not always true.

State assignment: Assign a unique binary code to each state of a finite state machine. State a collection of state variable whose value at any one time contains all the information about the past value necessary to account for future behaviour.

An evolved logic circuits: A logic circuit is evolved mean that the evolutionary algorithm started with randomly generated non-functional circuit and through evolution, finds a fully functional circuit. The circuit is evolved based on the test-and-assemble method.

#### Evolvable Hardware

A function set of logic gates, is a set of logic gates from which the circuit can be assembled. For example the AND-OR, the function set of logic gates contains AND, OR and NOT logic gates. In evolvable hardware any set of logic gate can be chosen. Each logic gate in a functional set of logic gates is encoded with integer.

#### Adaptation

The process of generating a set of behaviours that more closely match or predict a specific environmental regime. An increased ecological-physiological efficiency of an individual relative to others in the population. The response of an organism to the present stimulus and its present state. It is the total sum of behaviours of an organism that define the fitness of the organism to its present environment; thus it is the operative function against which selection operates.

#### allele

One of a set of possible values for a gene. In a binary string genome, the alleles are 0 and 1.

#### Chromosome

Rod-shaped bodies in the nucleus of cells, most visible particularly during cell division, which contain the hereditary units or genes. A data structure (e.g. binary bit-string or an array of integers), which holds a "string" of task parameters, or genes. In evolutionary algorithms, chromosome is often used to refer to a genome.

#### Crossover

In genetic algorithms, a reproduction operator which forms a new chromosome by combining parts of each of two "parent" chromosomes.

#### Ecosystem

Biological community of interacting organisms and their physical environment.

#### **Evolution**

The process of change which is assured given a reproductive population in which there are (1) varieties of individuals, with some varieties being (2) heritable, of which some varieties (3) differ in fitness (reproductive success).

#### **Evolutionary algorithms**

Search and optimisation techniques based on the principles of natural evolution.

#### Evolution strategy

A type of evolutionary algorithm developed in the early 1960s in Germany. It employs real-coded parameters, and in its original form, it relied on mutation as the search operator and a population of size one. Since then it has evolved to share many features with genetic algorithms.

#### **Evolutionary computation**

Encompasses methods of simulating evolution on a computer.

Extrinsic EHW the evolution is simulated in software, and only the elite chromosome (i.e. the configuring bit string) gets written. Thus the circuit is configured only once.

#### Exploration

The process of visiting entirely new regions of search space, to see if anything promising may be found there.

Exploitation: Local search. Exploration: Global search.

#### **Fitness**

A summation of the quality of environmental prediction by an organism throughout its range of regimes. The probability of or propensity for survival of an individual or population. A value assigned to an individual who reflects how well the individual solves the task at hand.

#### Genetic programming

Genetic algorithms applied to programs. Genetic programming is more expressive than fixed-length character string genetic algorithms, though genetic algorithms are likely to be more efficient for some classes of problems.

#### Gene

A unit of heredity located on a chromosome and composed of DNA. *Gene is* the smallest unit in a genome. In a binary string genome, the bits are genes. In an array of characters, each character in the array is a gene.

#### Genetic operator

A search operator acting on a coding structure that is analogous to a genotype of an organism (e.g. a chromosome).

#### Genotype

The sum of inherited characters maintained within the entire reproducing population. Often also used to refer to the genetic constitution underlying a single trait or set of traits.

#### Heredity

The transmission of characteristics from parent to offspring through the gametes.

#### Hyperspace

A Cartesian co-ordinate space of high dimension, typically higher than three dimensions.

#### Individual

A single member of a population. In evolutionary computation, each individual represents a potential solution to the problem.

**Intrinsic EHW** the circuit gets configured for each chromosome for each generation (on-line).

#### Mutation

A reproduction operator, which forms a new individual by making alterations (usually small) to the parent.

#### Natural selection

The result of competitive exclusion as organisms fills the available finite resource space.

#### Netlist

For an electronic circuit is a data structure consisting of unordered list that define both topology and sizing of the circuits.

#### Normal distribution

A probability distribution that approximates a bell-shaped curve in shape.

#### Offspring

An individual generated by any process of reproduction.

#### Phenotype

The behavioural expression of the genotype in a specific environment. The realised expression of the genotype.

#### Pleiotropy

The capacity of a gene to affect a number of different phenotypic characteristics.

#### Poisson distribution

A discrete probability distribution commonly used to define arrivals in a queuing system.

#### Polygeny

The circumstance where a single phenotypic is affected by multiple genes.

#### **Population**

A group of individuals which may interact together, for example, by producing offspring.

#### Probabilistic

Models developed under conditions of uncertainty.

#### Reproduction

The creation of a new individual from two parents (sexual reproduction). Asexual reproduction is the creation of a new individual from a single parent.

#### Reproduction operator

A mechanism, which influences the way in which genetic information is passed on from parent(s) to offspring during reproduction. Reproduction operators fall into three broad categories: mutation, crossover and reordering operators.

#### Search space

Generally, if the solution to a problem can be represented using a representation scheme R, then the search space is the set of all possible configurations, which may be represented in R.

#### Selection

The process by which some individuals in a population are chosen for reproduction, typically on the basis of favouring individuals with higher fitness.

#### **Species**

A group of similarly constructed organisms that is capable of interbreeding and producing fertile offspring. A population whose members are able to interbreed freely under natural conditions.

#### Stochastic

A situation in which imprecise or random events affect values of variables, so that results can be given only in terms of probabilities.

#### Chapter 1

#### INTRODUCTION

Chips that evolve and adapt to an environment

The processor inside a computer is designed to be a jack-of-all-trades and master of none, as people do many different things with their computers, from playing games to word processing. However, researchers are currently creating computer chips that can adapt themselves to particular software called Evolvable Hardware (EHW). Rather than being programmed, the chips learn as needed. The first likely use of the new chips will be in supercomputers or satellites, but eventually they will be used in everyday computers.

However, before this happens, the basics of designing chips using evolution need to be mastered.

Telegraph Connected, 8 April 2000 www.telegraph.co.uk

#### 1.1 Overview

This thesis addresses several problems in sequential circuit optimisation, that is, transformations on finite state machines which produce machines having equivalent behaviour, but whose implementations are either more economical, faster, or both. In particular, the focus of this thesis is a suite of algorithms and tools, which synthesize small, high performance realizations of finite state machines, given a suitable specification.

#### 1.1.1 Objectives

Biological organisms are among the most intricate structures known to man, exhibiting highly complex behavior through the massively parallel cooperation of huge numbers of relatively simple elements, the cells. As the development of computing systems approaches levels of complexity such that their synthesis begins to push the limits of human intelligence, more and more engineers are beginning to look at nature to find inspiration for the design. This thesis will present one such endeavor, notably an attempt to draw inspiration from biology in order to design novel digital circuits, endowed with a set of features motivated and guided by the behavior of biological systems: self-replication and self-repair.

The first phase of this research looks at the state assignment problem of automated synthesis of synchronized sequential circuits and highlights the importance of considering the genetic algorithm and its parameters and how it is implemented to solve the state assignment problem for logic synthesis and optimisation. The genetic algorithms (GA) approache to state assignment has been evaluated by comparing with both industry standard tools and other research published in this area [1].

The second goal of the research is to develop Evolvable Hardware (EHW) approach capable to design practical digital logic circuits.

In order to achieve this goal it was necessary to:

- 1. Investigate the evaluation process in the extrinsic gate-level evolvable hardware apparatus

- 2. Develop high-level self-adaptive EHW approach

- 3. Design an extrinsic EHW approach that is capable of evolving large benchmark circuits.

The proposed approach consists of four main stages. The first stage is concerned with the use of GA for the state assignment problem to compute optimal binary codes for each symbolic state to construct the state transition table of finite state machines (FSM). The second stage defines the subcircuits required to achieve the desired functionality. The third stage evaluates the subcircuits using extrinsic Evolvable Hardware. During the fourth stage, the final circuit is assembled. The obtained results compare favourably with those produced by manual methods and other methods based on heuristic techniques.

The focus of the research has mainly been directed towards traditional technology and applying evolutionary techniques to evolve new and hopefully

better circuits and thus prove the worth of EHW as a design technique. The EHW will then be compared with the traditional techniques.

The motivation behind the study of digital circuit evolution is to design circuits that are more efficient than the conventional designs, and then, to learn new principles of design.

Thus new methods and principles of evolving digital circuits are inferred.

#### 1.1.2 Generalities

Evolutionary Algorithms, as defined in [2] is a "collection of computational search, learning, optimization and modeling methods loosely inspired by biological evolution". Some of those methods are evolutionary programming (EP) [3], evolution strategies (ESs) [4] and genetic algorithms (GA) [5]. In the first part of this research genetic algorithms will be used for solving the state assignment problem of finite state machine. A more detailed description of the genetic algorithms and their use will be given in chapter 3. It is sufficient here to say that since their initial development in the 1970 genetic algorithms, as a tool of optimization, have had many successes in solving problems where the search space is huge. The fact that they evaluate in parallel many different solutions confers on them the ability to solve some optimization problems much faster than more conventional optimization techniques.

In the past, evolutionary algorithms methods have essentially been applied to software applications. It is only recently that those methods have been applied to the design of hardware circuits. Therefore in the second part of this research we use the evolutionary algorithms for the design of circuits. One of the main reasons for trying to design hardware circuits using alternative methods is to find some better circuits (for example smaller, faster or less power than those which could be designed using conventional techniques).

A circuit designer is limited by the set of mathematical models, the rules and techniques that he/she learned, whilst by freely exploring the space of all possible circuits new unconventional designs may be found. Of those

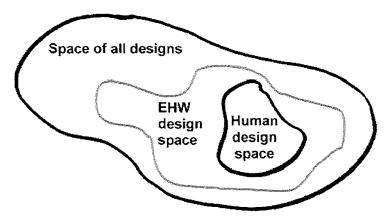

alternative methods, evolutionary computation, and more precisely genetic algorithms, come naturally to mind: they are very efficient methods for search in large spaces. The result of applying evolutionary algorithms to the design of hardware circuits is named Evolvable Hardware [1, 6]. There are presently two different trends in the field of EHW. On one side there are those who believe in a truly unconstrained evolution: the space of all possible circuits is freely explored. This approach can lead to spectacular results but also to failures. By tackling a too complex task the risks are high to the extent that no solution can be found [7]. On the other side there are those who perform hardware evolution within some constraints, generally by giving a structure to the circuits being evolved, thus reducing the size of the search space. The search space being smaller, the evolutionary process can explore it faster than with unconstrained evolution [1]. Some very interesting results have also been found, such as finding combinational logic circuits using fewer gates than what is obtained by using Karnaugh Maps and Boolean algebra or the Quine-McCluskey procedure [6].

Evolutionary techniques require evaluation and modification of large populations of individuals until a solution is found. For this reason, reprogrammable FPGAs (Field Programmable Gate Array) are usually the tool of choice, but not the only one, for EHW implementation [8].

#### 1.1.3 Evolutionary Electronics

Evolution of electronic circuits has been intensively investigated for the last decade. Evolutionary Electronics is a research area, which involved application of evolutionary algorithms in the domain of electronics. The main challenge of the area is the evolution of circuits for industrial applications and also to find methods to improve the performance of Evolutionary Algorithms in electronic circuit synthesis.

Evolutionary Electronics Circuit design applies the concepts of genetic evolution to the evolution of electronic circuits [9]. The main idea behind this research field is that each possible electronic circuit can be represented as an

individual or a chromosome of an evolutionary process, which performs standard genetic operations over the circuits. Due to the broad scope of the area, researchers have been focusing on different problems, such as optimization of combinational and sequential digital circuits [1, 10], synthesis of digital circuits [11], placement and routing [12], synthesis of passive and active analogue circuits [13], synthesis of operational amplifiers [14], and transistor size optimisation [15]. Table 1.1 summaries some relevant work on evolutionary Electronics. This is not a complete list of research work in the area, there are many other no less important work that have not been mentioned here. The study attends to identify the research application that started innovative trends in this area.

However, the evolutionary design of digital circuits is a process of evolving configurations of logic components for some prespectied computational program. Often the aim is for a highly efficient electronic circuit to emerge in a population of instances of the program. Digital electronic circuits have been evolved intrinsically [16] and extrinsically [17]. The former is associated with an evolutionary process in which each evolved electronic circuit is built and tested in hardware, while the latter refers to circuit evolution implemented entirely in software using computer simulations. The motivation behind the study of digital circuit evolution is to design electronic circuits that are more efficient than the conventional designs, and then, to learn new principles of design. It is well-accepted fact that to evolve circuits with increasing size is a difficult task even for evolution. However, the evolution of small circuits is feasible. The studies have revealed that often the evolved solutions are unusual in construction, and can be efficient in terms of number of gates used. Learning new principles of design is beneficial for the design of electronic circuits. Thus new methods and principles of evolving digital circuits are inferred.

Table 1.1 Some key publications in evolutionary electronics.

| Date | Authors                     | Application                                                                  |

|------|-----------------------------|------------------------------------------------------------------------------|

| 1991 | Louis and Rawilis [18]      | Evolution of basic digital function                                          |

| 1993 | H. De Garis [19]            | Introduction of the concept of<br>Evolvable Hardware                         |

| 1995 | Thompson et al. [9]         | Evolution of a hardware sensorimotor control structure                       |

| 1995 | Hemmi et al. [20]           | used of hardware description language<br>to evolve circuits                  |

| 1996 | Koza et al. [21]            | Evolution of low-pass filter and bipolar transistor amplifies                |

| 1997 | Miller et al. [6]           | Evolution of novel arithmetic digital circuits                               |

| 1998 | Zebulum et al. [22]         | Evolution of a digital circuit for CPU control                               |

| 1999 | Chongstitvatana et al. [23] | Learning finite state machine synthesis from partial input/output sequences. |

| 2000 | T. Kalganova [24]           | EHW Design for combinational logic circuits.                                 |

| 2002 | B. Ali et al. [1]           | Design of sequential logic circuit                                           |

# **ALL MISSING PAGES ARE BLANK**

IN

ORIGINAL

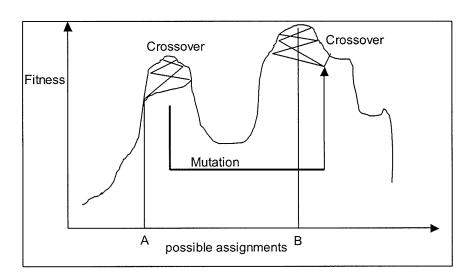

correct solution by concentrating on too small an area. That is, too much exploration means too much time, and too much exploitation means that the correct solution may not be found. Striking a good balance between exploration and exploitation is critical for a successful search algorithm.

Wasting time in unpromising areas of the search space may seem a small price to pay on the way to find the correct solution. Unfortunately, the size of the search space that arise in design domains is often so large that a human lifetime is short compared to the time needed by the fastest supercomputer to look at a significant fraction of the space. At the other extreme are algorithms that do no exploration and have knowledge available to solve the problem fast and directly. These algorithms make strong assumption about the search space and sufficient exploitable information is available to avoid searching. However, because these strong assumptions do not usually hold acrossdomain (search space) these algorithms work only on the particular space they were designed for and marginally on others.

In between these extremes of random and/or exhaustive search and no search, every other search algorithm makes assumptions of varying kinds about search space. These assumptions correspond to knowledge about the space and may be correct, incorrect, or misleading, implicit or explicit, and known or unknown, when used to search a particular space. This knowledge is exploited to guide exploration, speeding up search for generating a search is manifested in the set of generated solution.

Genetic algorithms belong to a class of algorithms, called blind search algorithms, which make the assumption that there is enough knowledge to compare two solutions and tell which is better [25]. There are different tasks when using EHW to evolve:

1. Because EHW are not subject to the limitations of human designers they can thus explore a much larger set of designs, maybe even the whole space of all designs (Figure 1.1).

Figure 1.1. Space of all designs.

- 2. The EHW design space might grasp a larger part of the space of all designs than the human design space.

- 3. Evolutionary Electronics deals with a huge search space, requiring, therefore powerful search techniques to handle the task. Naturally, when the search space is very large, only random search has some chance to succeed. Hence, with this new approach to circuit designs a search technique procedures have to be followed:

- The search space sampled by the algorithm must have its size limited.

- It is usually necessary to adapt the search technique to the particularities of the design problem.

#### 1.2 Scope of the Thesis

This section discusses the scope and limitations of the present body of work. This thesis focuses exclusively on sequential logic synthesis and outlines the use of the extrinsic EHW approach to evolve FSM. Both GA and EHW are combined together to produce optimal logic circuit. GA is used to optimise the state assignment problem. EHW is used to design the combinational parts of the desired circuit. The approach is tested on a number of FSMs. These circuits have been evolved using different functional sets of logic gates and

GA parameters. The sequential behaviour of FSMs is represented by a set of logic components.

We believe that an extension of each of the methods presented herein to extended sequential design is relatively straightforward. This is an area for future work. In addition, the algorithms in this thesis are all based on a single encoding model: the input-encoding model (described in detail in Chapter 4). This limits their effectiveness under certain cost metrics, because input encoding is only an approximation of optimal state encoding. As such, we expect that considerably better logic would result under these metrics from using a more precise model. In particular, a more potent model, namely output encoding could be substituted in the various steps, without disturbing the remainder of the synthesis path. As a result, input encoding is actually quite effective for this application.

Finally, algorithms presented here are computationally too expensive for the full range of sequential machines encountered in practice. Implicit methods, such as those introduced in this work, would extend its capacity enough to handle any practical design.

#### 1.3 The position of this thesis within the field

In preparing for this research program, it is intended to take a specific viewpoint: That small circuits evolved with as few constraints as possible may be of increased utility to engineering applications if they are properly understood. In addition to the factors governing a circuit's operation, understanding encompasses the influence an evolutionary design process has on its structure and properties, and whether altering the process for example by changing the types of basic element or evolutionary algorithm operators could improve the circuit in some way. It will be clear to the reader from the preceding pages that there are many ways of tackling this, and that some of the foundations have already been laid by the authors cited above. The first evolvable design suitable for general logic circuit, the first examples of extrinsic hardware evolution at the gate level, and the discovery and partial understanding of an entirely new form of evolved circuits. While the study

acknowledge the importance of large finite state machine benchmarks for the evolution of complex circuits, this work is intended to provide insights into the types of circuit at which evolution excels, and further foundations for the methodologies by which they can be produced. It is believed that the most appropriate starting point for achieving this is through the evolution and analysis of relatively small circuits. If computer time and memory limitations can be overcome, large design can be evolved.

#### 1.4 Outline of the thesis

The thesis is about relationship between redesign structure and search. The relationship has been studied in the context of digital circuit evolution. In general the thesis can be divided into two parts. The first summarizes the theory of logic design processing and introduces an information analysis by which the structure of a circuit is characterized. The analysis is applied to a well-investigated model of design and thus the theoretical finding is supported empirically.

The use of the evolutionary algorithms to the problem of digital circuits design is discussed in the second part of the thesis.

Three goals are pursued in this part:

Firstly, demonstrate the advantages of the method.

Secondly, to show how the study of the structure of design that originates from a particular optimization problem could help to improve the evolutionary search. Furthermore, to identify principles that help to overcome the problem of the very fast growth in the number of gates used in the target circuit as the number of inputs to the evolved logic function is increased.

Thirdly, special attention is paid to the role in digital circuit evolution.

Chapter 2 is a brief introduction to the problem of design of logic circuits. Further, it describes various forms of synchronous circuits, which are the focus of the bulk of the thesis. It begins with a discussion of conventional methods of digital design and closes with a description of logic synthesis tools needed for computer aided. It offers a general overview of sequential synthesis and traditional approaches. Provides a survey of digital circuit design and optimisation technique, which speed up the design cycle and enhance design quality. The chapter presents the basic definition necessary for understanding the work presented in this thesis. The chapter summarize the commercial tools available for design. Synthesis of finite state machines method for both two-level and multilevel logic implementation of the combination logic section of finite state machine is presented. Then, it presents one of the central themes of this thesis: the state assignment problem and previous approaches to this problem. The main contribution of the chapter is the algorithm for the state assignment problem that will be discussed further in chapter 4.

Chapters 3 introduce natural selection, evolutionary algorithm theory and compares evolutionary algorithm and other search algorithms. This sets the stage for describing the innovative powers of a genetic algorithm and elaborating on encoding and evaluation of design for genetic algorithms. Further the chapter will discuss evolvable hardware. It will show how evolvable hardware has emerged from the combination of evolutionary algorithm and flexible electronic devices. It will also give an overview of the different subdivisions of EHW and their applications. After reading this chapter, the reader should have an understanding of the domain of evolvable hardware and the particular problems involved.

Chapter 4 highlights the importance of considering the genetic algorithm and its parameters and how it is implemented to solve the state assignment problem for logic synthesis and optimization. The more general problem of logic circuit optimisation is explored. Synthesis based on a GA allows a

designer to minimise the actual area, power, or delay while performing state assignment. These GAs compensate for most of the unpredictability inherent in the logic reduction synthesis tools, providing a better measure of the circuit's characteristics. The genetic algorithm converges faster and finds better state assignment compared to previous reported methods. The genetic algorithm finds the best solutions for the encoding of all medium size MCNC benchmarks and tests result for these benchmarks are given. The synthesis based on the GA approach results in designs with the smallest area to date. Test results on standard benchmarks are given and compared with previously reported results.

Chapter 5 Studies the evolutionary design of combinational and sequential logic circuits, particularly the sequential circuit. Thus digital circuits are evolved using evolutionary algorithms. The structure of the resulting circuits is investigated and it is shown that the principles of evolving digital circuits are valid. In this chapter an approach based on an evolutionary algorithm to design sequential logic circuits with minimum number of logic gates is proposed.

Chapters 6 outlines the use of the extrinsic evolvable hardware approach to evolve finite state machines. Both the genetic algorithm and Evolvable Hardware are combined together to produce optimal logic circuits. A GA is used to optimise the state assignment problem. EHW is used to design the combinational parts of the desired circuit. The approach is tested on a number of finite state machines from MCNC benchmark sets. These circuits have been evolved using different functional sets of logic gates and GA parameters. The results show promise for the use of this approach as a design method for sequential logic circuits.

**Chapter** 7 contains concluding remarks, which review the contribution of this work and include topics for further research.

#### 1.5 Summary

With the continuous increase in the complexity of electronic circuits, there is increased demand for effective methodologies for the design of such electronic circuits. These increases in complexity together with the increasing number of design objective (e.g. low power, high throughput, small area) provide the designer with a very hard task. For that reason there is a demand for effective ECAD tools, which perform some of the design tasks leaving the designer to concentrate on performance optimisation issues.

The complexity of the electronic design search space has encouraged using all computer-based techniques in the design procedure. One such technique, which is used in this thesis, is called Genetic Algorithms. These algorithms have shown a high degree of flexibility in dealing with problems with complex and computationally hard Problems, such as the electronic circuit design problem.

This thesis describes investigations carried out in order to develop a genetic based digital circuit design/synthesis ECAD tool. The investigations have led to the development of a novel custom genetic algorithm for the structural design of circuits. A number of circuit specific genetic operators have been produced and their use has been investigated together with conventional genetic operators.

# Chapter 2

#### REVIEW OF THE LOGIC DESIGN PROCESS

#### 2.1 Introduction

The impact of Very Large Scale Integration (VLSI) circuits in modern life can be seen in various electronic facilities. Over the years, growth in the complexity of VLSI design has enable designer to include well over a million transistors on each chip. Designers are faced with the daunting task of packing more functionality into a smaller area and creating a circuit that operates faster than the previous generation. Design Automation (DA) technique play an invaluable role in this complex process.

The first phase of this project looks at the state assignment problem of automated synthesis of synchronized sequential circuits. Automated synthesis for digital logic is rapidly increasing in importance in industrial design. This is due to the huge increase in possible circuit size over the past few years, making it extremely difficult to design efficiently by hand. Synthesis tools such as Synopsis free the designer to operate at a high level, performing the transition to lower level of design automatically, along with relevant optimisations. Optimisation of sequential circuits was first studied in detail in the late 1950s and 1960s [26], but has recently increased in importance.

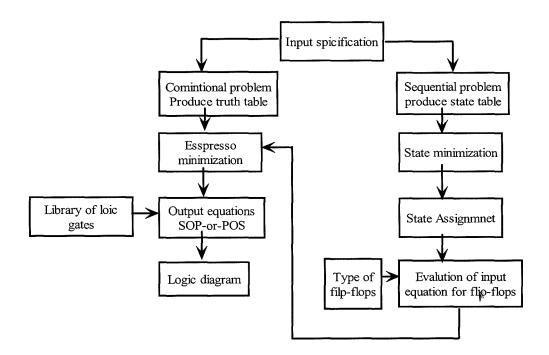

This chapter starts by introducing the reader to the relevant subject area. The concept of logic synthesis can be defined as the process of transforming a verbal description of required functionality into a working circuit. Traditionally, it has been divided into combination and sequential synthesis. The research is focused on sequential synthesis and in particular the state assignment problem due to its impact on the complexity of the resulting circuit. The details of the algorithm implemented for the state assignment

problem using genetic algorithm are also given. This algorithm has been evaluated by comparing it with both standard industrial tools and other research published in this area.

#### 2.2 Overview of Optimal Logic Synthesis

The benefits of automating the logic design process may be compromised if the result does not meet its area, speed, or power constraints, while optimising the design trade-offs. Effort is made to enable the design tools to make informed decisions as well as an expert designer could [27,28]. Therefore, a critical aspect of automatic logic synthesis is the optimization problem of deriving a high-quality design from the initial specification. The accepted optimization criteria for multi-level logic are to minimize some convex function of:

- 1. Area occupied by the logic gates and interconnects.

- 2. The Critical Path Delay of the longest path through the logic.

- The Degree of Testability of the circuit, measured in terms of the

percentage of faults covered by a specified set of test vectors, for an

appropriate fault model (e.g. single stuck-at faults, multiple stuck-at

faults, etc.).

- 4. Power consumed.

This minimization is to be performed while simultaneously satisfying upper or lower bound constraints placed on these physical quantities. While humans are superbly equipped to solve such problems once they are clearly formulated, the sheer mass of detail in VLSI designs makes the use of synthesis tools imperative.

Delay constrained area minimization has an immediate effect on practical microchip design. The design has to physically fit on the chip, which typically is of the order of 1cm square or less. We note also that area minimization has an economically important impact on yield, because net yield is known to decrease exponentially with the size of the chip. Alternatively, algorithms for area-constrained delay minimization are often used to maximize performance.

Another criterion, which is increasingly important especially for mobile technologies such as laptop, computers, and cellular phones, is to minimize the power consumption of the final circuit. The area, delay and power of a design before layout are estimated using models, which predict the effects of physical design, based on the cells and nets in the final design. Often power is minimized by just making the design slower, but transformations exist which reduce power while not increasing delay [132].

Another important part of integrated circuit design is the manufacturing test, which determines if a fabricated chip works as expected. A connection (wire) is untestable (or redundant) if replacing the connection with a constant value does not affect the functionality of the circuit.

If the connection is not testable, it is called redundant and when a redundant connection is removed, a smaller circuit is formed. There is the further problem that redundancies interfere with the production line testing of the integrated circuit. Therefore, another goal for logic synthesis is to produce designs with no redundancies.

Synthesis tools are also in an ideal position to tackle the testing problem. These tools create and alter designs, so that they can easily modify them for testability [28]. It makes sense for synthesis tools to insert the special structures needed for test, if any, and then optimise the whole design, including the test structures, for minimum speed and area penalty. Similarly, it is logical for synthesis tools to produce vectors that are inherently integrated with a design's test structures, and to minimize the vector set required to test the design. Thus the marriage of synthesis and test can achieve a fully automated test solution, and serves to move test forward in the design cycle.

The design of the optimal circuit that meets all of these constraints is a difficult problem due to the tremendous number of potential solutions for even a small set of logic equations. The size of VLSI circuits makes its logic synthesis a difficult optimization problem, which usually requires automated

tools for practical designs. The next sections outline the tools needed to design and efficiently utilize computer aided design tools for automatic logic synthesis.

## 2.3 Logic Synthesis with ECAD Tools

Electronic Computer-Aided Design (ECAD) of microelectronic circuits is concerned with the development of computer programs for the automated design and manufacture of integrated electronic systems, with emphasis today on VLSI circuits [29]. Synthesis of VLSI circuits involves transformation of the specification of circuit behaviour into mask-level layout, which can be fabricated using VLSI manufacturing processes, usually a number of representations between abstract behaviour and mask-level layout. Optimisation strategies, both manual and automatic are vital in VLSI synthesis in order to meet the required specifications. However, the optimisation problems encountered in VLSI synthesis are typically NP hard. Therefore, solutions to the optimisation problem are incorporated in heuristic strategy, the development of which requires a thorough understanding of the problem at hand. Thus, automatic optimisation—based VLSI synthesis has evolved in to a rich and exciting area of research.

Direct application of synthesis in industry has been a significant drive force for research in ECAD. Simple marketing principles that other factors being equal, a product available sooner would capture a large share of market and would remain in use longer. The desire to reduce time to market has led to the initial investment of considerable money and effort into the development of ECAD tools capable of producing designs competitive with the best manual design. Today, constantly shrinking geometry and increasingly reliable manufacturing process have led to complex systems being implemented on a single chip making the use of ECAD tools commonplace and manufactory. In its turn, the rapid automation of the VLSI design phase has allowed companies to keep pace with advances in other areas of VLSI like computer architecture and manufacturing. As a consequence of this rapid development

in VLSI technology, it is currently possible to produce an ASIC, microprocessors and other type of circuits that contain millions of transistors. ASIC designer and recent advances in systems on chip (SOC) make the use of ECAD tools commonplace and mandatory.

#### 2.4 VLSI Design Flow

Design is the process of translating an idea into a product that can be manufactured. In the design of electronics this is simply a product formed from electronic equipments, software, and electromechines. Effective design allows this translation to be done quickly cheaply and accuracy to produce a product that is commercially viable, competitive, fit for purposes, without problem and adaptable.

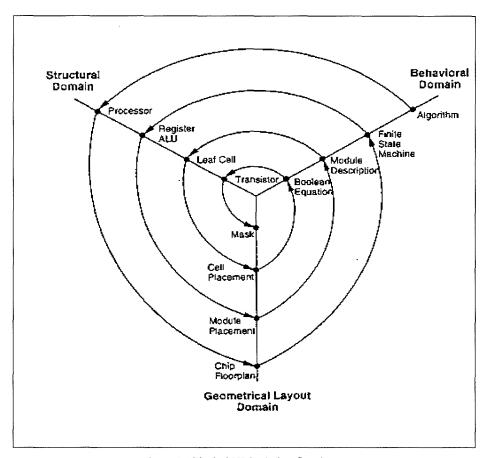

The design process, at various levels, is usually evolutionary in nature. It starts with a given set of requirements. Initial design is developed and tested against the requirements. When the requirements are not met, the design has to be improved. If such improvement is either not possible or too costly, then the revision of requirements and its impact analysis must be considered. The Y-chart shown in Figure 1.2 illustrates a design flow for most logic chips, using design activities on three different axes (domains), which resemble the letter Y [30]. The Y-chart consists of three major domains, namely:

- Behavioural domain,

- Structural domain,

- Geometrical layout domains.

The design flow starts from the algorithm that describes the behaviours of the target chip. The corresponding architecture of the processor is first defined. It is mapped onto the chip surface by floor planning. The next design evolution in the behavioural domain defines finite state machines, which are structurally implemented with functional modules such as registers and arithmetic logic units (ALUs).

These modules are then geometrically placed onto the chip surface using ECAD tools for automatic module placement followed by routing, with a goal of minimising the interconnection area and signal delays.

Figure 2.1. Typical VLSI design flow in three domains (Y-chart representation).

The third evolution starts with a behavioural module description. Individual modules are then implemented with leaf cells. At this stage the chip is described in terms of logic gates (leaf cells), which can be placed and interconnected by using a cell placement & routing program. The last evolution involves a detailed Boolean description of leaf cells followed by a transistor level implementation of leaf cells and mask generation. In standard-cell based design, leaf cells are already pre-designed and stored in a library for logic design use.

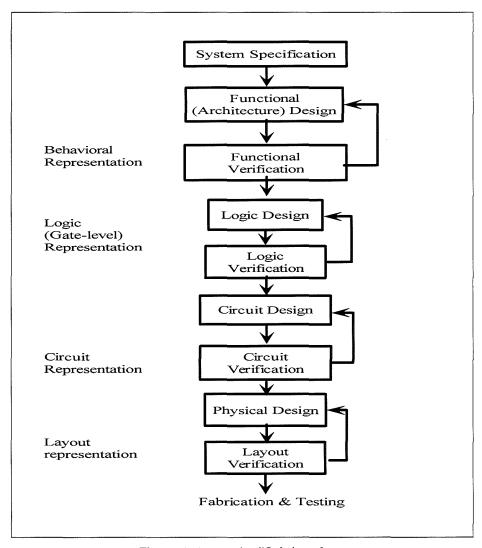

Figure 2.2. A more simplified view of VLSI design flow.

Figure 2.2 provides a more simplified view of the VLSI design flow; taking into accounts the various representations, or abstractions of design behavior, logic, circuit and mask layout. Note that the verification of design plays a very important role in every step during this process. The failure to properly verify a design in its early phases typically causes significant and expensive re-design at a later stage, which ultimately increases the time-to-market. Although the design process has been described in linear fashion for simplicity, in reality