## A Study of Arithmetic Circuits and the Effect of Utilising Reed-Muller Techniques

Zhigang Guan

A thesis submitted in partial fulfilment of the requirements of Napier University for the degree of Doctor of Philosophy in the Department of Electrical, Electronic & Computer Engineering

September 1995

# CONTAINS PULLOUTS

#### Abstract

Reed-Muller algebraic techniques, as an alternative means in logic design, became more attractive recently, because of their compact representations of logic functions and yielding of easily testable circuits. It is claimed by some researchers that Reed-Muller algebraic techniques are particularly suitable for arithmetic circuits. In fact, no practical application in this field can be found in the open literature.

This project investigates existing Reed-Muller algebraic techniques and explores their application in arithmetic circuits. The work described in this thesis is concerned with practical applications in arithmetic circuits, especially for minimizing logic circuits at the transistor level. These results are compared with those obtained using the conventional Boolean algebraic techniques. This work is also related to wider fields, from logic level design to layout level design in CMOS circuits, the current leading technology in VLSI. The emphasis is put on circuit level (transistor level) design. The results show that, although Boolean logic is believed to be a more general tool in logic design, it is not the best tool in all situations. Reed-Muller logic can generate good results which can't be easily obtained by using Boolean logic.

For testing purposes, a gate fault model is often used in the conventional implementation of Reed-Muller logic, which leads to Reed-Muller logic being restricted to using a small gate set. This usually leads to generating more complex circuits. When a cell fault model, which is more suitable for regular and iterative circuits, such as arithmetic circuits, is used instead of the gate fault model in Reed-Muller logic, a wider gate set can be employed to realize Reed-Muller functions. As a result, many circuits designed using Reed-Muller logic can be comparable to that designed using Boolean logic. This conclusion is demonstrated by testing many randomly generated functions.

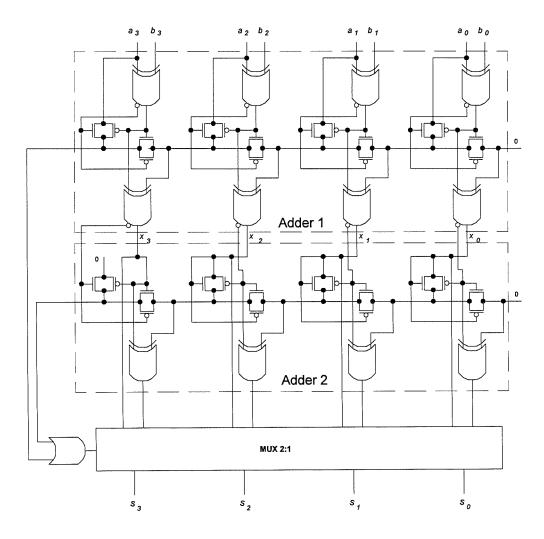

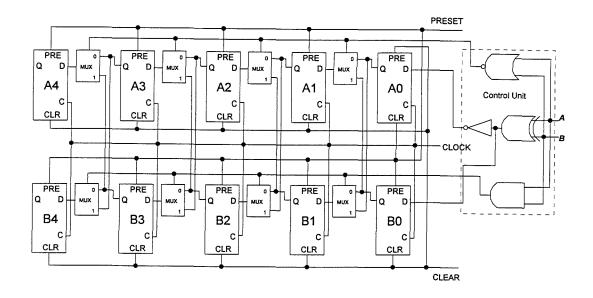

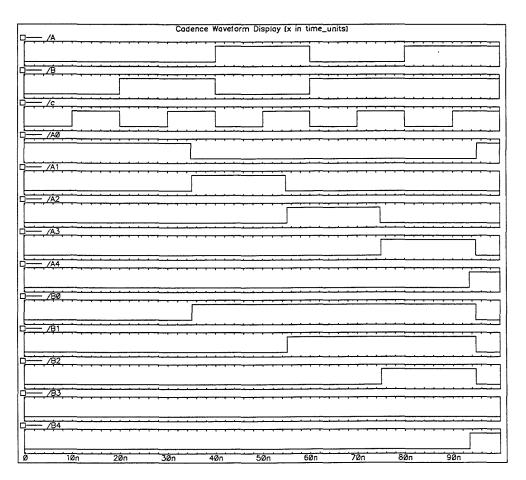

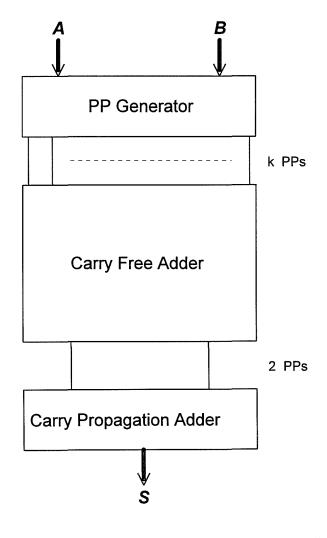

The main aim of this project is to develop arithmetic circuits for practical application. A number of practical arithmetic circuits are reported. The first one is a carry chain adder. Utilising the CMOS circuit characteristics, a simple and high speed carry chain is constructed to perform the carry operation. The proposed carry chain adder can be reconstructed to form a fast carry skip adder, and it is also found to be a good application for residue number adders. An algorithm for an on-line adder and its implementation are also developed. Another circuit is a parallel multiplier based on 5:3 counter. The simulations show that the proposed circuits are better than many previous designs, in terms of the number of transistors and speed. In addition, a 4:2 compressor for a carry free adder is investigated. It is shown that the two main schemes to construct the 4:2 compressor have a unified structure. A variant of the Baugh and Wooley algorithm is also studied and generalized in this work.

## Acknowledgements

I would like to express my gratitude to Prof. Almaini for his good guidance, patience, understanding, friendship and encouragement throughout this work.

I would also like to express my gratitude for the studentship offered to me by the Department of Electrical, Electronic and Computer Engineering, Napier University.

I would like to thank Mr. P. Thomson for his guidance and kindly help during the first stage of this project. I also offer my sincere thanks to my former colleagues Ms. L. Xu, Ms. L. McKenzie, and Mr. N. Zhuang. Our good-natured discussions and their advice are invaluable. Thanks are also due to the staff members in Dept of EECE, Napier University, for the generous support given to me.

Finally, this thesis is dedicated to my wife Qiao Zhang, my daughter Xiaoqiao Guan, and my parents Yanjun Guan and Zhifang Wang, I could not have completed this thesis without their unending support and help.

## Declaration

No portion of the work referred to in this thesis has been submitted in support of an application of another degree or qualification of this or any other university or institution of learning.

Zhigang Guan

## List of Abbreviations

| BSD   | Binary Signed-Digit           |  |  |  |

|-------|-------------------------------|--|--|--|

| CFA   | Carry Free Adder              |  |  |  |

| CMOS  | Complementary MOS             |  |  |  |

| CPA   | Carry Propagation Adder       |  |  |  |

| DAG   | Directed Acyclic Graph        |  |  |  |

| ECAD  | Electronic CAD                |  |  |  |

| ESOP  | Exclusive or SOP              |  |  |  |

| EXOR  | EXclusive OR                  |  |  |  |

| FA    | Full Adder                    |  |  |  |

| FPGA  | Field Programmable Gate Array |  |  |  |

| IC    | Integrated Circuit            |  |  |  |

| KRM   | Kronecker Reed-Muller         |  |  |  |

| LCA   | Logic Cell Array              |  |  |  |

| lsb   | least significant bit         |  |  |  |

| LSI   | Large scale integration       |  |  |  |

| MOS   | Metal Oxide Silicon           |  |  |  |

| msb   | most significant bit          |  |  |  |

| NMOS  | N channel MOS                 |  |  |  |

| PLA   | Programmable Logic Array      |  |  |  |

| PMOS  | P channel MOS                 |  |  |  |

| POS   | Product Of Sums               |  |  |  |

| PP(s) | Partial Product(s)            |  |  |  |

| PPG   | PP Generator                  |  |  |  |

| RBA   | Redundant Binary Adder        |  |  |  |

| RM    | Reed-Muller                   |  |  |  |

| RNS   | Residue Number System         |  |  |  |

| SD    | Signed-Digit                  |  |  |  |

| SOG   | Sea Of Gates                  |  |  |  |

| SOP   | Sum Of Products               |  |  |  |

| VLSI  | Very Large Scale Integration  |  |  |  |

| XOR   | eXclusive OR                  |  |  |  |

| XPLA  | XOR PLA                       |  |  |  |

|       |                               |  |  |  |

## List of Accompanying Material

- Z. Guan, A. E. A. Almaini, and P. Thomson, "A simple and high speed CMOS carry chain adder architecture", *Int. J. Electronics*, Vol. 75, No. 4, Oct. 1993, pp. 743-752.

- Z. Guan, "Logic Realization Using Mixed Representations Based on Reed-Muller Forms", Proc. IEE Colloquium on Synthesis and Optimization of Logic Systems, London, March 14, 1994, pp. 2/1-2/4.

- Z. Guan, P. Thomson, and A. E. A. Almaini,"A Parallel CMOS 2's Complement Multiplier Based on 5:3 Counter", *Proc. IEEE Int. Conf. Comput. Design*, Boston, Oct. 10-12, 1994, pp. 298-301.

- 4). Z. Guan, and A.E.A. Almaini,"One Bit Adder Design Based on Reed-Muller Expansions", *Int. J. Electronics*, to be published.

# Contents

| Abstract                      | i   |

|-------------------------------|-----|

| Acknowledgements              | ii  |

| Declaration                   | iii |

| List of Abbreviations         | iv  |

| List of Accompanying Material | v   |

## **Chapter 1: Introduction**

| 1.1 Reed-Muller Logic   | 1 |

|-------------------------|---|

| 1.2 Arithmetic Circuits | 3 |

| 1.3 Objective           | 4 |

| 1.4 Thesis Outline      | 5 |

## **Chapter 2: Reed-Muller Logic**

| 2.1 Introduction                                       | 7  |

|--------------------------------------------------------|----|

| 2.2. The algebra of GF(2)                              | 8  |

| 2.3 Zero Polarity RM Canonical Expansion               | 10 |

| 2.4 Relationships Between $a_i$ and $b_i$ Coefficients | 12 |

| 2.5 Fixed Polarity RM Canonical Expansions             | 13 |

| 2.6 Relationships Between $a_i$ and $c_i$ Coefficients |    |

| 2.7 Kronecker RM(KRM) Canonical Expansions             | 17 |

| 2.8 Relationships Between $a_i$ and $e_i$ Coefficients | 18 |

| 2.9 Inconsistent Forms                                 | 20 |

| 2.10 Dual Forms of RM Expansions                       | 20 |

| 2.11 Map Method                                        | 23 |

| 2.11.1 Folding Technique                               | 24 |

| 2.11.2 Map Minimization |    |

|-------------------------|----|

| 2.12 Tabular Method     |    |

| 2.13 Summary            | 36 |

## Chapter 3: CMOS Implementation of Logic Circuits

| 3.1 Introduction                            | 38 |

|---------------------------------------------|----|

| 3.2 CMOS Circuits                           | 39 |

| 3.3 Switching Network Theory                | 43 |

| 3.4 Some Techniques for Fast MOS circuits   | 47 |

| 3.5 PLA Implementation                      | 49 |

| 3.6 Gate Implementation                     | 51 |

| 3.7 Transistor Implementation               | 53 |

| 3.8 Mixed Representations Based on RM logic | 59 |

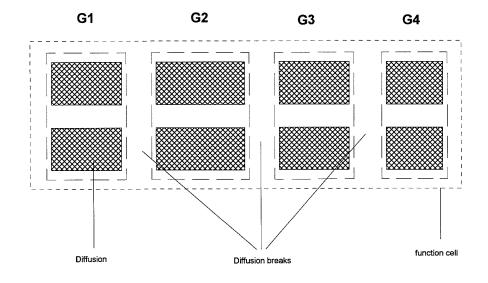

| 3.9 Layout Evaluation                       | 61 |

| 3.10 Testing of RM circuits                 | 65 |

| 3.11 Summary                                | 69 |

|                                             |    |

## Chapter 4: Number Systems and Two Operand Adders

| 4.1 Introduction                           | 71 |

|--------------------------------------------|----|

| 4.2 Number Systems for Arithmetic Circuits | 72 |

| 4.2.1 2's Complement Number System         | 72 |

| 4.2.2 Signed-Digit Number System           | 73 |

| 4.2.3 Residue Number System                | 75 |

| 4.3 Review of Two Operand Adders           |    |

| 4.4 Design Methodology                     | 81 |

| 4.5 Carry Lookahead Circuit                | 85 |

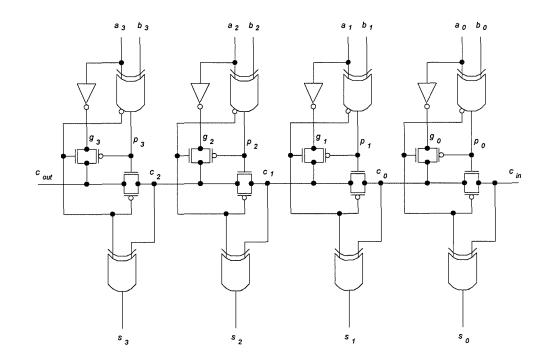

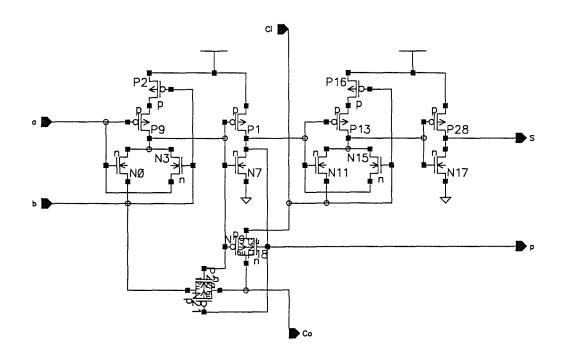

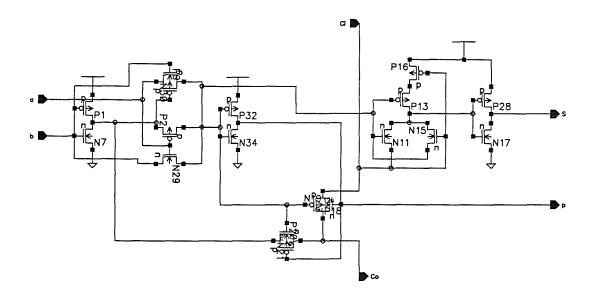

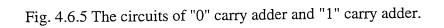

| 4.6 Carry Chain Adder                      | 90 |

| 4.7 Residue Adders | 101 |

|--------------------|-----|

| 4.8 On Line Adder  |     |

| 4.9 Summary        | 112 |

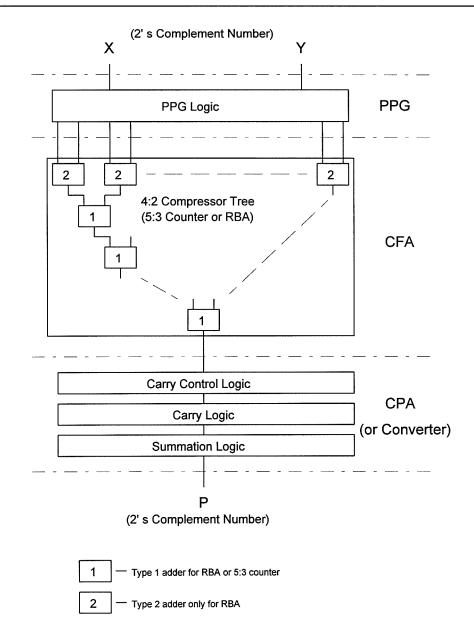

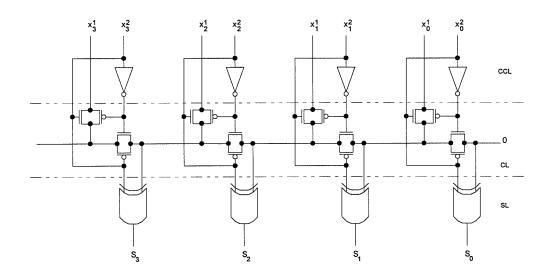

## Chapter 5: Carry Free Adders and Parallel Multipliers

| 5.1 Introduction                                       | 113 |

|--------------------------------------------------------|-----|

| 5.2 Review of Multipliers                              | 114 |

| 5.3 A General Structure for Parallel Multiplier        | 118 |

| 5.4 Carry Free Adders                                  | 120 |

| 5.5 Redundant Binary Adder(RBA)                        | 122 |

| 5.6 Conversion between 2's Complement and RBSD Numbers | 125 |

| 5.7 5:3 Counter                                        | 126 |

| 5.8 A Unified Structure for 4:2 Compressor             | 131 |

| 5.9 Implementation Comparison and Evaluation           | 132 |

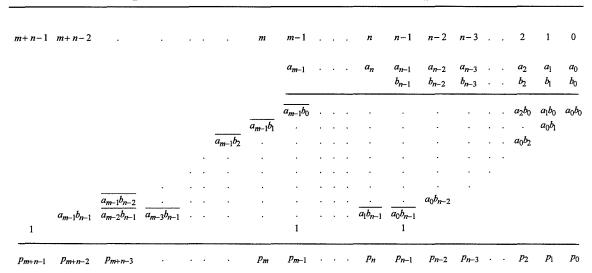

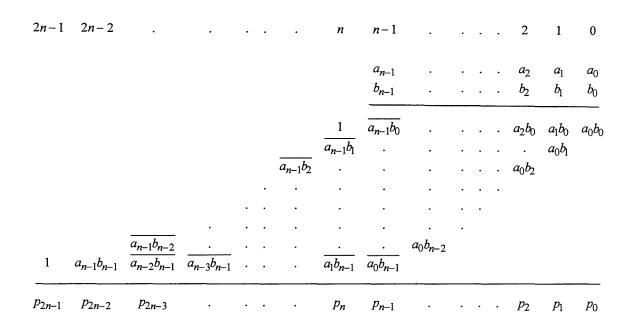

| 5.10 A Variant of Baugh and Wooley Algorithm           | 139 |

| 5.11 Parallel Multiplier based on 5:3 Counter          | 144 |

| 5.12 Summary                                           | 147 |

|                                                        |     |

## **Chapter 6: Conclusion**

| 6.1 Summary of Results | 149 |

|------------------------|-----|

| 6.2 Future Work        |     |

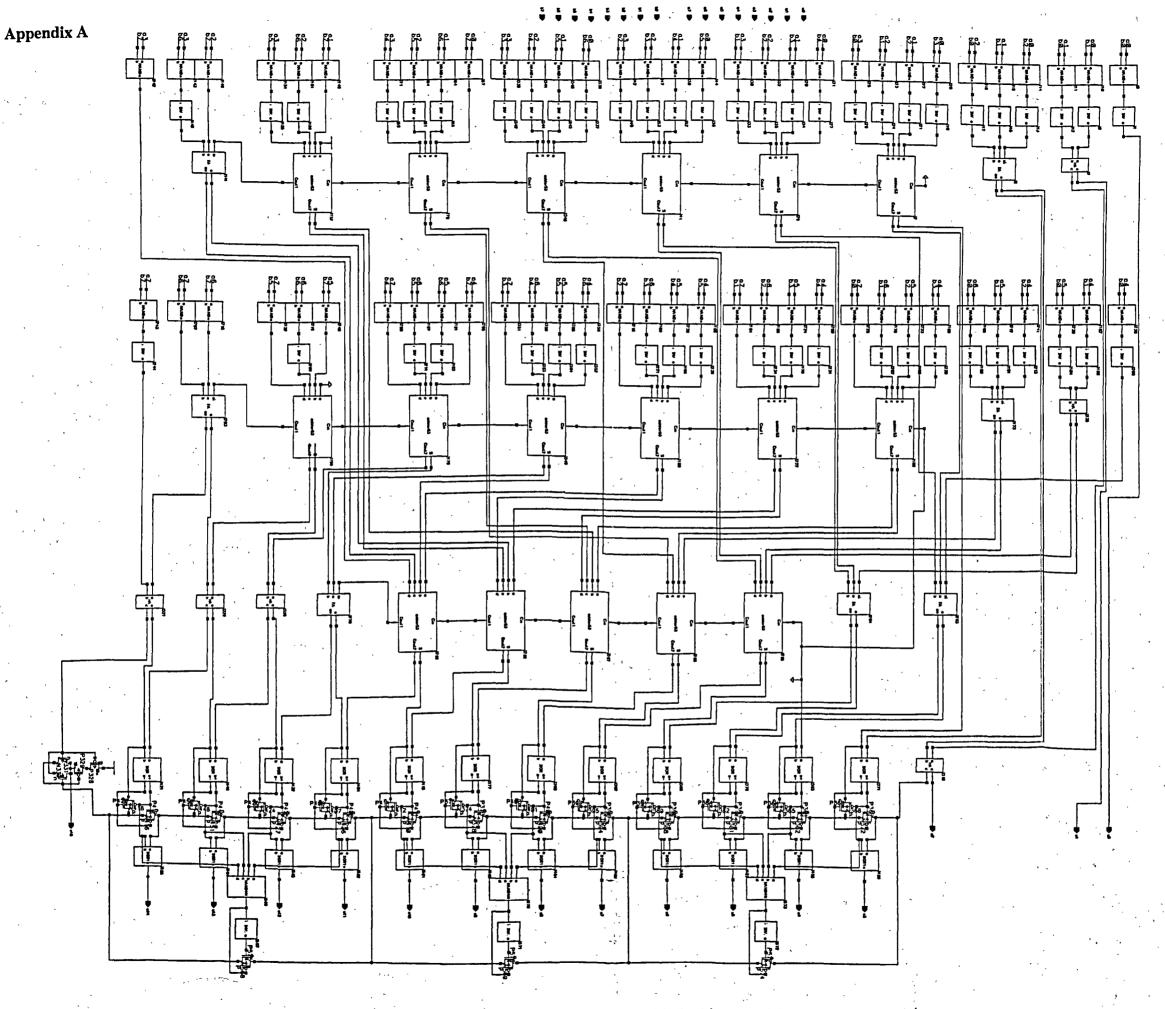

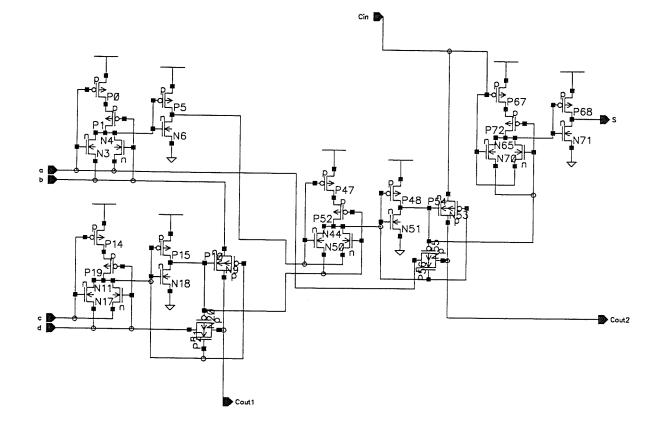

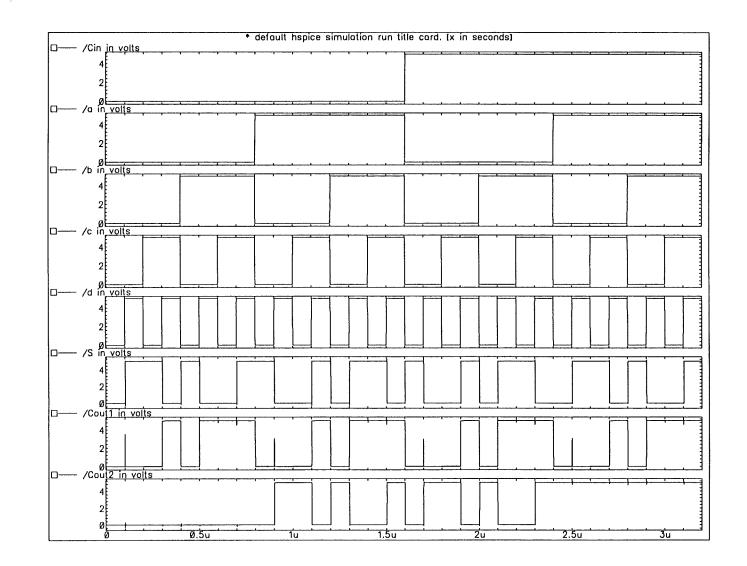

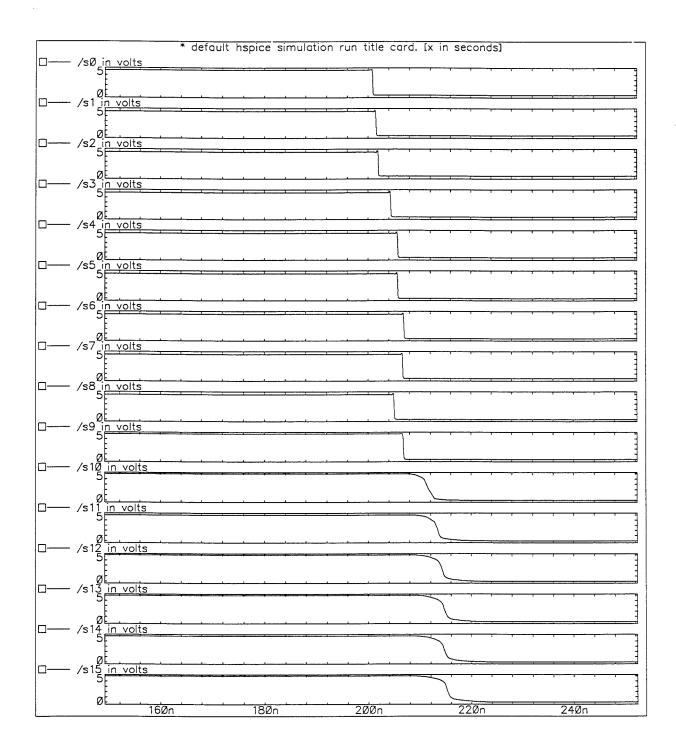

Appendix A: The schematics and simulations of a 8×8 parallel multiplier based on 5:3 counter

#### References

....

## Chapter 1

# Introduction

#### **1.1 Reed-Muller Logic**

Reed-Muller logic is an algebraic technique for logic circuit design based on AND and Exclusive OR (Modulo 2 arithmetic) operations. There is no universal definition and name for Reed-Muller logic. In the literature, it can be found that many different names are used, such as exclusive OR-switching function[Wu 82], EXOR logic[Besslich 83], Reed-Muller expansion of Boolean functions[Harking 90], Reed-Muller logic[Almaini 91], Reed-Muller algebraic techniques[Green 91B], Reed-Muller representation (expansion, form) of Boolean logic[Saul 92], modulo-2 expressions[Lui 92], AND-EXOR expression[Sasao 93B], Reed-Muller polynomial[Tran 93A], etc.. All these names are often used to describe the same thing, that is, at first, a logic function is represented in exclusive OR sum of products instead of inclusive OR sum of products, and then, the function is minimized by employing certain rules based on two basic operations, AND and Exclusive OR.

In this thesis, Reed-Muller logic, Reed-Muller expansion, Reed-Muller function, the Reed-Muller domain, etc. are employed. In contrast, Boolean logic, Boolean expansion, Boolean function, the Boolean domain, etc. are used to describe the traditional Boolean logic design where a function is represented in inclusive OR sum of products.

This technique was first introduced by Zhegalkin in 1927. He described a special kind of Exclusive Sum of Products (ESOP), which includes only uncomplemented Boolean variables. Later, Reed[Reed 54] and Muller[Muller 54] used ESOP for logic circuit design and error detection, since this time ESOP expressions have been called Reed-

Muller expressions (expansions, representations, forms, etc.) in the literature because Zhegalkin's work, written in Russian, was unknown[Steinbach 93].

Reed-Muller logic, as an alternative means in logic circuit design, can be employed to describe an arbitrary switching function completely. Systematic methods to simplify a logic function in the Reed-Muller domain have been developed[Muller 54, Wu 82, Green 86, 91B, Tran 87, 89, Almaini 91]. In the Boolean domain, a group of coefficients for a given logic function in its canonical form have certain physical meanings. Normally, "0" indicates that the output of a circuit is low, and "1" indicates that the output of a circuit is high. The coefficients directly correspond to a truth table that defines the function completely. In the Reed-Muller domain, the coefficients for a given logic function in its canonical form do not have certain physical meanings. In general, a logic function in the Reed-Muller domain is derived from a corresponding function in the Boolean domain via coefficient conversion.

For a long time, It had been conjectured that the realization of a class of logic functions in Reed-Muller expansions was more economical than the conventional Sum of Products (SOP), its counterpart in the Boolean domain. Later, this conjecture is proved mainly in Sasao and Besslich's work[Sasao 90, Sasao 93A, Sasao 93B]. In their work, many statistical data are used to show that two level Reed-Muller expansions, in general, require fewer products to represent a given logic function than SOP, the conventional two level Boolean expansion. These functions include arithmetic functions, randomly generated functions, symmetric functions, etc.. Consequently, a logic function in Reed-Muller expansion with less products can often generate a more economical circuit.

A lot of precious work about Reed-Muller logic, especially in theory, has been done in the past. Some results may be feasible for commercial products. The first automatic logic synthesis system to make use of the mixed-polarity Reed-Muller expansion is GATEMAP[Pitty 88, Salmon 89]. GATEMAP concurrently maintains three different representations of each logic function throughout all stages of its operation. These three representations are: 1). sum-of-products of the function; 2). sum-of-products of the inverse of the function; 3). mixed-polarity of the function. Finally, the best one is chosen to implement the function. A wide variety of functions are tested by GATEMAP. Reed-Muller equations are found to be normally of comparable size to the sum-of-products, with exceptions being where the Reed-Muller equations are significantly smaller.

Another main advantage of Reed-Muller logic considered by many researchers is that, when a logic circuit is realized with Reed-Muller expansion in two level fixed polarity form, it requires a short test set to detect a single stuck-at fault (stuck-at 0 and stuck-at 1) in the circuit, and the test set is independent of its actual function being realized[Reddy 72]. Based on the same principle of Reddy's, the function-independent test set for detecting single stuck-at fault and single bridging fault (AND and OR bridging faults) is explored[Bhattacharya 85, Damarla 89].

Although Reed-Muller logic has the two obvious advantages over the conventional Boolean logic, it is still unpopular compared with the applications in the Boolean Domain. Many researchers believed that the main reason for this is lack of efficient algorithms for its minimization[Besslich 83, Saul 90, Sarabi 92]. Therefore, most of the previous work done has been devoted mainly to focus on various algorithms to minimize a given logic function in the Reed-Muller domain and convert between the two domains in the most efficient way[Wu 82, Besslich 83, Green 96, 91B, Tran 87, 89, Helliwell 88, Saul 90, 91, 92, Almaini 91, Sasao 93A, B, McKenzie 93].

#### **1.2 Arithmetic Circuits**

Since the inception of digital computers, much effort has been directed towards the search for faster and simpler arithmetic techniques. Because of the high hardware cost, the earlier computers consisted only of simple and economical arithmetic circuits, such as adder, multiplier, etc.. Many complex arithmetic operations were accomplished by software.

With the advance of microelectronics, especially in VLSI technology, many complex arithmetic circuits have become feasible and common. These arithmetic circuits consist not only of dividers, square roots, matrix multipliers and trigonometric processors for general purpose or scientific calculation, but also of some special arithmetic processors for digital signal processing, such as, convolvers and FFT processors.

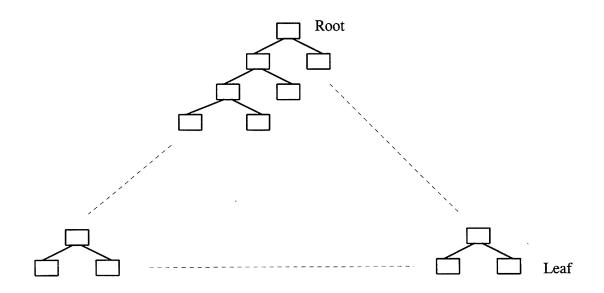

The earlier approach to designing arithmetic devices concentrated mainly on simple and high-speed circuits. With the development of VLSI technology, in order to deal with the increasing complexity of design, fabrication and test, regularity, modularity, regular and local connection are also emphasized. This is because, a regular and modular circuit not only is easily realized in VLSI, but also benefits testing. In addition, a regular and modular circuit can be easily pipelined, which will increase the throughput of a system in overlapped fashion.

The previous study of many researchers shows that, a lot of complex arithmetic operations, in practice, can be decomposed into two simple and basic operations, addition and multiplication [Hwang 79, Urquhart 84, Joseph 84, Scott 85, Koren 93]. Based on this, arithmetic circuit study may be classified into two categories. One is to attempt to study basic arithmetic circuits, such as adders and multipliers, and

minimize them not only at a higher level, but also at a lower level, such as logic level, circuit level, and layout level. This study is closely related to a logic design tool, for example, Boolean logic or Reed-Muller logic. The other is to attempt to investigate some complex arithmetic circuits and minimize them at a higher level, such as system level or architectural level, in which it is assumed that the basic components, adders, multipliers, and registers, etc., have been minimized. This study is rarely related to the logic design tool. Therefore, the implementation of many complex arithmetic processors is influenced directly by the performance of the adder and the multiplier. Owing to this reason, addition and multiplication have been the most widely studied, and many practical algorithms and implementations for various adders and multipliers have been presented.

It should be mentioned that subtraction and division also are very important basic operations. Subtraction can be achieved by addition in 2's complement number without any additional hardware. Division is often studied at a higher level, rather than at logic level or circuit level, this is because division is inherently composed of a sequential series of addition and subtraction. Consequently, the implementation of a divider, ultimately, depends heavily on the adder. In other words, compared with other arithmetic circuits, studying the adder and multiplier not only is emphasized at a higher level based on number systems, mathematical rules, etc., but also is emphasized at logic level and circuit level for their actual implementations.

Addition and multiplication also can be classified into fixed-point operation and floating-point operation. Float-point operation is more complex than fixed-point operation, but it is often studied at a higher level rather than at logic level and its implementation is still based on the implementation of fixed-point operation. Therefore, in this project, only fixed-point adders and multipliers are discussed, because they are more closely related to logic and circuit optimization.

In addition, only binary logic will be considered in this work. Although multi-valued logic has many theoretical advantages, its practical application is widely limited because of the shortage of reliable and stable basic components. Also, many algorithms in binary logic can be steadily developed into their counterparts in multi-valued logic.

#### **1.3 Objective**

"It is well-known that many useful circuits such as arithmetic units and parity checkers are heavily XOR oriented and it is more economical to implement their modulo-2 expressions" [Lui 92, Helliwell 88, Perkowski 89, 90, Saul 91, 92, 93,

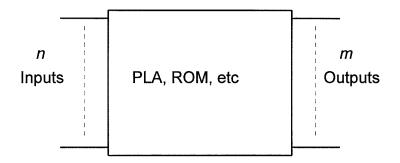

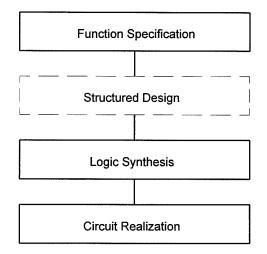

Sarabi 92, Csanky 93, Lester 93]. In fact, except for modulo 2 sum, few successful examples can be found relating to practical arithmetic circuits. One of the main reasons for this may be that, in most of the previous work about Reed-Muller logic, the minimization of functions is carried out without regard to target technology. Because the implementation complexity of Reed-Muller logic differs from that of Boolean logic, it is difficult to estimate and compare the results of Reed-Muller logic with that of Boolean logic accurately if only the number of products (literals) is employed. Also, arithmetic functions are established based on PLA or ROM implementation, and there is no architectural or structural design when using these functions. In this way, the results can not be easily generalized and therefore, they are not often employed in practical applications.

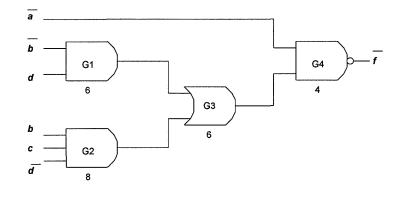

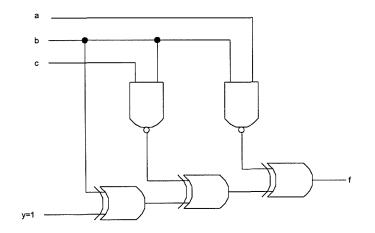

In this project, logic circuit optimization using Reed-Muller techniques is explored, and compared with Boolean techniques in MOS circuits, especially in CMOS circuits. The comparison is carried out mainly at the circuit level (transistor level), instead of the gate level, and the results are measured by the number of transistors. This makes the comparison more practical in actual designs. That is, one important difference from most previous work is that, it is desirable to know the minimum circuits more than the most compact logic functions in this work.

The use of Reed-Muller techniques for the synthesis of arithmetic circuits is studied. The circuits consist mainly of adders and parallel multipliers which are more closely related to circuit optimization, and the results are compared with that based on Boolean logic. This helped to gain greater insight into the subject of arithmetic operations, to evaluate the suitability of Reed-Muller techniques, and ultimately to develop more efficient arithmetic circuits.

#### **1.4 Thesis Outline**

Chapter 2 reviews the background theory of Reed-Muller logic that is used in later chapters. Representation of Reed-Muller logic for logic functions is first introduced. Secondly, the basic operations of Reed-Muller logic are described. Finally, some algorithms to minimize Reed-Muller functions are studied.

Chapter 3 describes basic circuits in CMOS. In order to compare Reed-Muller logic with Boolean logic in CMOS circuits, *switching network theory* is first introduced. Reed-Muller functions and Boolean functions realized in static CMOS circuit style are studied and compared. This study is explored from the gate level to the layout level,

but mainly at the transistor level. The main result about testing Reed-Muller circuits is reviewed. The possibility to minimize Reed-Muller circuits is investigated.

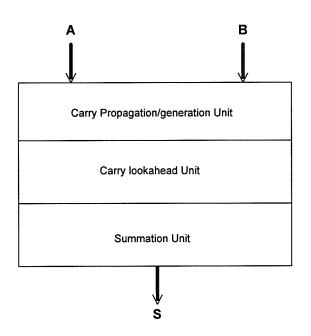

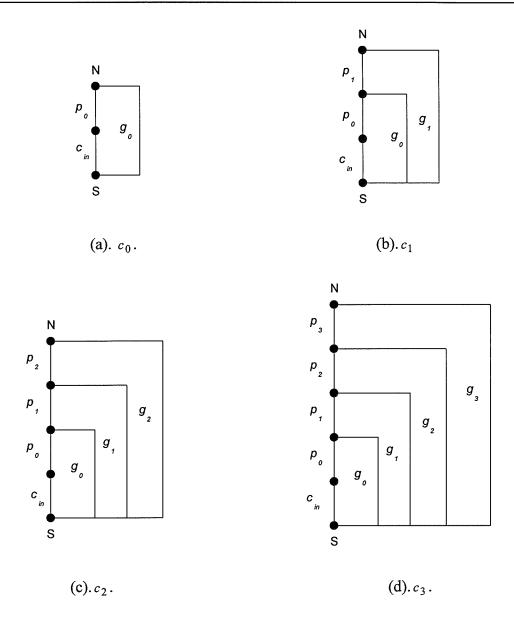

Chapter 4 first introduces some commonly used number systems and reviews the previous work about two operand adders, and then the design methodology for a general arithmetic circuit is discussed. Later, the possibility of using Reed-Muller logic to improve the carry lookahead circuit, as an example, is investigated. A simple and fast CMOS carry chain adder architecture is presented. This design can be reconstructed for the carry-skip adder, and is also developed for residue number adders. Finally, an algorithm for the on-line adder and its implementation are proposed.

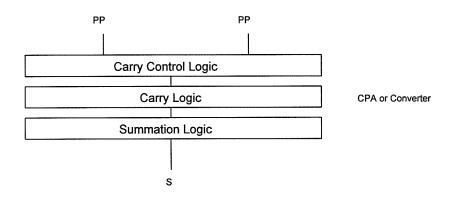

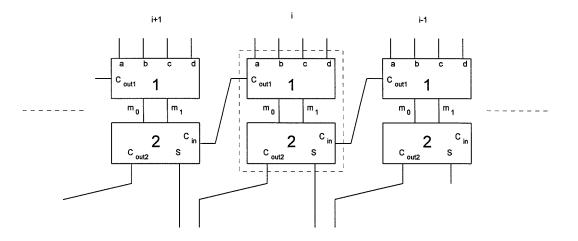

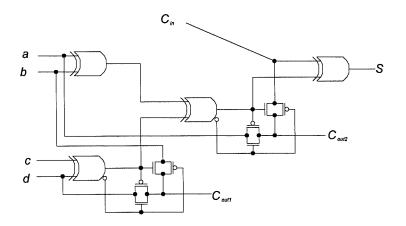

Chapter 5 commences with a review of the main results of multipliers proposed previously by other researchers. Parallel multipliers in the review are emphasized. A general structure for parallel multipliers is described and carry free adders are discussed. Two main types of the most widely used carry free adder modules, the redundant binary adder and the 5:3 counter, are investigated. A unified structure for these two modules is explored. Comparison and evaluation based on a survey of the literature is presented. Finally, a parallel multiplier based on the 5:3 counter is proposed. A variant of the Baugh and Wooley algorithm is generalized in the proposed design.

Chapter 6 concludes the thesis by summarising the main findings and contributions. Some related issues to be further explored for future study are suggested.

## **Chapter 2**

# **Reed-Muller Logic**

#### 2.1 Introduction

Reed-Muller (RM) logic, as an alternative means for logic design, is based on two basic operations in modulo 2 arithmetic: modulo 2 addition and modulo 2 multiplication. These two operations are identical to Boolean Exclusive-OR (EXOR or XOR) operation and AND operation. The resulting algebra is that of the finite or Galois field GF(2). This mode of representation supports the familiar mathematical operations such as matrices, transforms, polynomials, etc.[Green 86]. The resulting circuits are much easier to test than their counterparts in the Boolean domain[Reddy 72].

Unlike the situations in the Boolean domain, there exist a great deal of canonical expansions[Davio 78, Green 91A, Sasao 93B] in the RM domain, this makes it more difficult to minimize a logic function in the RM domain than in the Boolean domain. In addition, for a given logic function, its canonical expansions in the Boolean domain correspond directly to a truth table that completely specifies this function. For a logic function in the RM domain, there is no similar relationship between its canonical expansions and a truth table. This means that, no general means, like a truth table in the Boolean domain, can be used to specify a logic problem in the RM domain initially. In general, a RM function is derived from a Boolean function by a coefficient conversion.

In this chapter, the background theory of RM logic is introduced. This shall be used in subsequent chapters.

#### 2.2 The algebra of GF(2)

The definitions for the two basic operation in GF(2) are shown in Table 2.2.1. Assume that a, b, and c are two-valued variables, and symbols " $\oplus$ " and " $\cdot$ " represent modulo 2 addition (XOR operation) and modulo 2 multiplication (AND operation), respectively. The symbol " $\cdot$ " for AND operation can be missed if no confusion arises, i.e.,  $a \cdot b = ab$ .

| (1). Modulo 2 addition. |              | (2). Modulo 2 | multiplication. |

|-------------------------|--------------|---------------|-----------------|

| a b                     | $a \oplus b$ | a b           | $a \cdot b$     |

| 0 0                     | 0            | 0 0           | 0               |

| 0 1                     | 1            | 0 1           | 0               |

| 1 0                     | 1            | 1 0           | 0               |

| 1 1                     | 0            | 1 1           | 1               |

Table 2.2.1. Arithmetic operation tables of GF(2).

Some basic laws can be described as follows

| 1. Closure la | $a \oplus b$ a | nd $a \cdot b$ are a | lso two-value | (2.2.1) |

|---------------|----------------|----------------------|---------------|---------|

|---------------|----------------|----------------------|---------------|---------|

2. Associative laws  $a \oplus b \oplus c = (a \oplus b) \oplus c = a \oplus (b \oplus c)$

$a \cdot b \cdot c = (a \cdot b) \cdot c = a \cdot (b \cdot c) \tag{2.2.2}$

- 3. Distributive laws  $a \cdot (b \oplus c) = a \cdot b \oplus a \cdot c$  (2.2.3)

- 4. Commutative laws  $a \oplus b = b \oplus a, \quad a \cdot b = b \cdot a$  (2.2.4)

5. Identities

$$a \oplus 0 = a, a \cdot 1 = a$$

(2.2.5)

It is easily seen that these five laws are similar to that in Boolean algebra, the difference is that operator " $\oplus$ " is used to replace operator "+", where "+" is the inclusive OR operation, simply called OR operation.

There are two distinct operations which are quite different from that in Boolean algebra, they are:

6.

$$a \oplus a = 0$$

(2.2.6)7. $a \oplus 1 = \overline{a}$ (2.2.7)

$a \oplus a = 0$  is also called inverse operation, namely, every element is its own additive inverse. This means that addition and subtraction are the same in modulo 2 operation, i.e., a = -a.

The two distinct operations lead to very significant differences in the resulting algebra, and consequently in logic circuit design, implementation, and test aspects. From (2.2.6) and (2.2.7), other important properties can be derived as follows

$$a \oplus b = \overline{a} \oplus \overline{b} \tag{2.2.8}$$

$$\overline{a} \oplus b = a \oplus \overline{b} = \overline{a \oplus b} = 1 \oplus a \oplus b \tag{2.2.9}$$

(2.2.8) and (2.2.9) present flexibility in logic circuit implementation. According to (2.2.8), AND gates can be replaced by more economical NAND gates. (2.2.9) shows that electrical polarity is easy to adjust for a given logic circuit realized in RM expansion.

There exist many other operations for RM expansions, most of them can be derived from these basic operations 1~7. For example,  $\bar{a} \oplus a = 1$  can be easily deduced from equations (2.2.6) and (2.2.7).

Connectives between inclusive OR (OR) and exclusive OR (XOR) are:

$$\overline{ab} + a\,\overline{b} = a \oplus b \tag{2.2.10}$$

$$a+b=a\oplus b\oplus ab \tag{2.2.11}$$

$$f_1 a + f_2 \ \bar{a} = f_1 a \oplus f_2 \ \bar{a} \tag{2.2.12}$$

Equation (2.2.12) is often termed Shannon's decomposition, it can be also written as

$$f_1 a + f_2 \bar{a} = f_1 a \oplus f_2 \bar{a} = f_1 \oplus (f_1 \oplus f_2) \bar{a} = (f_1 \oplus f_2) a \oplus f_2$$

(2.2.13)

#### 2.3 Zero Polarity RM Canonical Expansion

A given logic function with n variables can be described by a truth table that is in its vector form

$$A = \begin{bmatrix} a_0 & a_1 & a_2 & \cdots & a_{2^n - 1} \end{bmatrix}$$

where  $a_i \in \{0,1\}$ , termed Boolean coefficients or  $a_i$  coefficients, represent the output values of a truth table.

In the Boolean domain, the disjunctive canonical expansion, or so called sum of product (SOP) canonical expansion, can be used for representing a given logic function. The expansion is based on minterm  $m_i$ , and it forms an equivalent algebraic expression to the truth table, it is

$$f(x_{n-1}, \dots, x_1, x_0) = \sum_{i=0}^{2^n - 1} a_i m_i = a_0 m_0 + a_1 m_1 + \dots + a_{2^n - 1} m_{2^n - 1}$$

(2.3.1)

where  $\sum$  represents logical summation (OR operation).

If each of the n variables is restricted to appear only in true form, and also a coefficient vector is defined as

$$B = \begin{bmatrix} b_0 & b_1 & b_2 & \cdots & b_{2^n - 1} \end{bmatrix}$$

where  $b_i \in \{0,1\}$ , termed  $b_i$  coefficients, then, a matrix operation of *n* vectors with a form  $\begin{bmatrix} 1 & x_i \end{bmatrix}$  is written as

$$\begin{cases} [1 \ x_0 \ ]^*[1 \ x_1 \ ]^*[1 \ x_2 \ ]^* \cdots * [1 \ x_{n-1} \ ] \rbrace \cdot B \\ = [1 \ x_0 \ x_1 \ x_1 x_0 \ x_2 \ x_2 x_0 \ \cdots \ \cdots \ x_{n-1} \cdots x_2 x_1 x_0 \ ] \cdot B \\ = [b_0 \ b_1 x_0 \ b_2 x_1 \ b_3 x_1 x_0 \ b_4 x_2 \ b_5 x_2 x_0 \ \cdots \ \cdots \ b_{2^n - 1} x_{n-1} \cdots x_2 x_1 x_0 \ ] \end{cases}$$

(2.3.2)

where "\*" indicates the Kronecker product[Green 86]. An example is used to illustrate the Kronecker product. Assume that two 2×2 matrixes

$$A = \begin{bmatrix} a_{00} & a_{01} \\ a_{10} & a_{11} \end{bmatrix}, \qquad B = \begin{bmatrix} b_{00} & b_{01} \\ b_{10} & b_{11} \end{bmatrix}$$

(2.3.3)

the Kronecker product of them is

$$A * B = \begin{bmatrix} a_{00} \begin{bmatrix} B \end{bmatrix} & a_{01} \begin{bmatrix} B \end{bmatrix} \\ a_{10} \begin{bmatrix} B \end{bmatrix} & a_{11} \begin{bmatrix} B \end{bmatrix} \end{bmatrix}$$

(2.3.4)

In general, if A is a  $p \times q$  matrix and B is a  $r \times s$  matrix, then A \* B is a  $pr \times qs$  matrix. The "\*" operation is associative but not commutative, i.e.,

$$A * B * C = A * (B * C) = (A * B) * C$$

(2.3.5)

$$A * B \neq B * A \tag{2.3.6}$$

If the XOR operation is used to be connectives between the elements in (2.3.2), an expansion can be represented as

$$f(x_{n-1}, \dots, x_1, x_0) = b_0 \oplus b_1 x_0 \oplus b_2 x_1 \oplus b_3 x_1 x_0 \oplus b_4 x_2 \oplus b_5 x_2 x_0 \oplus \dots \oplus b_{2^n - 1} x_{n-1} \dots x_2 x_1 x_0$$

(2.3.7)

Equation (2.3.7) is the so-called zero polarity RM expansion or positive polarity RM expansion, which can be used to describe any given logic function with n variables.

#### 2.4 Relationships Between $a_i$ and $b_i$ Coefficients

Unlike  $a_i$  coefficients (Boolean coefficients),  $b_i$  coefficients don't correspond to the output of a truth table, that is,  $b_i$  coefficients can't be obtained directly from a truth table, because  $b_i$  coefficients don't have a definite logical significance.  $a_i$  coefficients and  $b_i$  coefficients can be transformed to each other. This transform is based on a transform matrix  $T_1$  that is defined as

$$T_1 = \begin{bmatrix} 1 & 0\\ 1 & 1 \end{bmatrix} \tag{2.4.1}$$

For a two variable function, the transform can be written as

$$b_0 = a_0$$

$$b_1 = a_0 \oplus a_1$$

$$b_2 = a_0 \oplus a_2$$

$$b_3 = a_0 \oplus a_1 \oplus a_2 \oplus a_3$$

(2.4.2)

In matrix form, this transform is expressed as

$$B = T_2 \cdot A = \begin{bmatrix} b_0 \\ b_1 \\ b_2 \\ b_3 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 \end{bmatrix} \cdot \begin{bmatrix} a_0 \\ a_1 \\ a_2 \\ a_3 \end{bmatrix} \quad \text{over GF}(2) \quad (2.4.3)$$

where  $T_2$  is a transform matrix for two variables. It is easily verified that

$$T_{2} = T_{1} * T_{1} = \begin{bmatrix} T_{1} & 0 \\ T_{1} & T_{1} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 \end{bmatrix}$$

(2.4.4)

In general, the transform from  $a_i$  coefficients to  $b_i$  coefficients in matrix form can be expressed as

$$B = T_n \cdot A \tag{2.4.5}$$

and

$$T_n = T_1 * T_{n-1} = T_1 * T_1 * \dots * T_1$$

*n* times (2.4.6)

Furthermore, it can be established that

$$T_1^{-1} = T_1 \tag{2.4.7}$$

so that

$$T_n^{-1} = T_n \tag{2.4.8}$$

this means that the matrix is self-inverse. Thus

$$A = T_n \cdot B \tag{2.4.9}$$

#### 2.5 Fixed Polarity RM Canonical Expansions

The zero polarity RM canonical expansion is just one of a large number of possible expansions. If each of the n variables is restricted to appear in its true form or its

complemented form, but not both, this leads to  $2^n$  combinations from *n* variables, which correspond to  $2^n$  so called fixed polarity RM canonical expansions. Like the zero polarity expansion, a coefficient vector *C* is defined as

$$C = \begin{bmatrix} c_0 & c_1 & c_2 & \cdots & c_{2^n - 1} \end{bmatrix}$$

where  $c_i \in \{0,1\}$ , termed  $c_i$  coefficients.

Assume that  $\dot{x_i}$  represents  $x_i$  or  $\overline{x_i}$ , but not both, in a consistent way throughout a logic function. Thus

$$\{ \begin{bmatrix} 1 & \dot{x_0} \end{bmatrix} * \begin{bmatrix} 1 & \dot{x_1} \end{bmatrix} * \begin{bmatrix} 1 & \dot{x_2} \end{bmatrix} * \dots * \begin{bmatrix} 1 & \dot{x_{n-1}} \end{bmatrix} \} \cdot C$$

$$= \begin{bmatrix} 1 & \dot{x_0} & \dot{x_1} & \dot{x_1} & \dot{x_0} & \dot{x_2} & \dot{x_2} & \dot{x_0} & \cdots & \dot{x_{n-1}} \cdots & \dot{x_2} & \dot{x_1} & \dot{x_0} \end{bmatrix} \cdot C$$

$$= \begin{bmatrix} c_0 & c_1 & \dot{x_0} & c_2 & \dot{x_1} & c_3 & \dot{x_1} & \dot{x_0} & c_4 & \dot{x_2} & c_5 & \dot{x_2} & \dot{x_0} & \cdots & \cdots & c_{2^n-1} & \dot{x_{n-1}} \cdots & \dot{x_2} & \dot{x_1} & \dot{x_0} \end{bmatrix}$$

$$(2.5.1)$$

Similarly to that for the zero polarity RM expansion, the vector (2.5.1) can be written as

$$f(x_{n-1}, \dots, x_1, x_0) = c_0 \oplus c_1 \dot{x_0} \oplus c_2 \dot{x_1} \oplus c_3 \dot{x_1} \dot{x_0} \oplus c_4 \dot{x_2} \oplus c_5 \dot{x_2} \dot{x_0} \oplus \dots \oplus c_{2^n-1} \dot{x_{n-1}} \dots \dot{x_2} \dot{x_1} \dot{x_0}$$

(2.5.2)

Clearly, the zero polarity RM expansion is a special case of the  $2^n$  fixed polarity RM expansions.

#### 2.6 Relationships Between $a_i$ and $c_i$ Coefficients

It is possible to employ similar matrix techniques as above to transform between  $a_i$  coefficients and  $c_i$  coefficients.

For convenience to describe the following transformation, a polarity number is defined as

$$P = (p_{n-1}p_{n-2} \cdots p_0)_2$$

where  $p_i \in \{0,1\}$ , corresponding to the position of  $x_i$ . This is a binary representation of the decimal integer *P*. If the true form of  $x_i$  is used, then  $p_i = 0$ ; and if its complemented form is used, then  $p_i = 1$ . For example, for a three variable function,  $P = 3 = (011)_2$ , this means that  $x_2$  is in its true form and both  $x_1$  and  $x_0$  are in their complemented form.

Two basic transform matrixes are defined as

$$W_0 = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}, \qquad W_1 = \begin{bmatrix} 0 & 1 \\ 1 & 1 \end{bmatrix}$$

(2.6.1)

Clearly,

$$W_0 = T_1$$

(2.6.2)

since the fixed polarity expansions contain the zero polarity expansion. Thus, a generalized matrix W can be expressed as

$$W_p = W_{p_{n-1}} * W_{p_{n-2}} * \dots * W_{p_0}$$

(2.6.3)

where  $W_{p_i} = W_0$  or  $W_1$ , depending on the form (true or complemented) of each variable. Thus, the transform from  $a_i$  coefficients to  $c_i$  coefficients is

$$C = W_p \cdot A \tag{2.6.4}$$

For example, if  $p_i = 3 = (011)_2$ , then

$$C = W_3 \cdot A = \{W_0 * W_1 * W_1\} \cdot A \tag{2.6.5}$$

Thus

$$\begin{bmatrix} c_{0} \\ c_{1} \\ c_{2} \\ c_{3} \\ c_{4} \\ c_{5} \\ c_{6} \\ c_{7} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 1 & 0 & 1 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} a_{0} \\ a_{1} \\ a_{2} \\ a_{3} \\ a_{4} \\ a_{5} \\ a_{6} \\ a_{7} \end{bmatrix}$$

(2.6.6)

$c_i$  coefficients can be also obtained from  $b_i$  coefficients. That is

$$C = W_p \cdot A = W_p \cdot T_n \cdot B = Z_p \cdot B \tag{2.6.7}$$

Similarly to  $W_p$ ,  $Z_p$  is expressed as

$$Z_p = Z_{p_{n-1}} * Z_{p_{n-2}} * \dots * Z_{p_0}$$

(2.6.8)

$Z_0$  and  $Z_1$  are

$$Z_{0} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}, \qquad Z_{1} = \begin{bmatrix} 1 & 1 \\ 0 & 1 \end{bmatrix}$$

(2.6.9)

From equation (2.6.7), it can be seen that

$$Z_{0} = W_{0} \cdot T_{1} = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$$

(2.6.10)

$$Z_1 = W_1 \cdot T_1 = \begin{bmatrix} 0 & 1 \\ 1 & 1 \end{bmatrix} \cdot \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix} = \begin{bmatrix} 1 & 1 \\ 0 & 1 \end{bmatrix}$$

(2.6.11)

#### 2.7 Kronecker RM(KRM) Canonical Expansions

RM canonical expansion can be further extended if some of the variables can be allowed to appear in both true and complemented form in a consistent way. This means that another basis vector  $\begin{bmatrix} x_i & \overline{x_i} \end{bmatrix}$  is included along with  $\begin{bmatrix} 1 & x_i \end{bmatrix}$  and  $\begin{bmatrix} 1 & \overline{x_i} \end{bmatrix}$  that are used only to generate the fixed polarity expansions.

By selecting one of these three bases for each variable, it will generate  $3^n$  distinct expansions which are called Kronecker RM (KRM) canonical expansions. The KRM expansions contain the  $2^n$  fixed polarity RM expansions and some of mixed polarity RM expansions.

Similarly to the previous approach, a coefficient vector for KRM expansions is defined as

$$E = \begin{bmatrix} e_0 & e_1 & e_2 & \cdots & e_{2^n - 1} \end{bmatrix}$$

where  $e_i \in \{0,1\}$ , termed  $e_i$  coefficients.

Also, a polarity number is defined as

$$M = (m_{n-1}m_{n-2}\cdots m_0)_3$$

where  $m_i \in \{0,1,2\}$ . This is a ternary representation of the decimal integer M. If  $\begin{bmatrix} 1 & x_i \end{bmatrix}$  is used, then  $m_i = 0$ ; if  $\begin{bmatrix} 1 & \overline{x_i} \end{bmatrix}$  is used, then  $m_i = 1$ ; and if  $\begin{bmatrix} x_i & \overline{x_i} \end{bmatrix}$  is used, then  $m_i = 2$ .

For example, when n=3 and  $M=15=(120)_3$ , i.e.,  $1\times 3^2 + 2\times 3^1 + 0\times 3^0 = 15$ , the KRM expansion can be obtained by

$$\left\{ \begin{bmatrix} 1 & \overline{x_2} \\ 1 & \overline{x_1} \end{bmatrix} * \begin{bmatrix} x_1 & \overline{x_1} \\ 1 & x_1 \end{bmatrix} * \begin{bmatrix} 1 & x_0 \end{bmatrix} \right\} \cdot E$$

$$= \left[ x_1 & x_1 x_0 & \overline{x_1} & \overline{x_1} x_0 & \overline{x_2} x_1 & \overline{x_2} x_1 x_0 & \overline{x_2} \overline{x_1} & \overline{x_2} \overline{x_1} x_0 \end{bmatrix} \begin{bmatrix} e_0 \\ e_1 \\ e_2 \\ e_3 \\ e_4 \\ e_5 \\ e_6 \\ e_7 \end{bmatrix}$$

$$= \left[ e_0 x_1 & e_1 x_1 x_0 & e_2 \overline{x_1} & e_3 \overline{x_1} x_0 & e_4 \overline{x_2} x_1 & e_5 \overline{x_2} x_1 x_0 & e_6 \overline{x_2} \overline{x_1} & e_7 \overline{x_2} \overline{x_1} x_0 \end{bmatrix}$$

(2.7.1)

Similarly to the previous cases, the vector (2.7.1) is expressed as

$$f(x_{2}, x_{1}, x_{0}) = e_{0}x_{1} \oplus e_{1}x_{1}x_{0} \oplus e_{2} \overline{x_{1}} \oplus e_{3} \overline{x_{1}}x_{0} \oplus e_{4} \overline{x_{2}}x_{1}$$

$$\oplus e_{5} \overline{x_{2}}x_{1}x_{0} \oplus e_{6} \overline{x_{2}} \overline{x_{1}} \oplus e_{7} \overline{x_{2}} \overline{x_{1}}x_{0}$$

(2.7.2)

#### **2.8** Relationships Between $a_i$ and $e_i$ Coefficients

Like  $c_i$  coefficients,  $e_i$  coefficients can be derived from  $a_i$  coefficients or  $b_i$  coefficients by employing similar matrix techniques. In order to obtain  $e_i$  coefficients from  $a_i$  coefficients, three basic matrixes are introduced, they are

$$Q_0 = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}, \quad Q_1 = \begin{bmatrix} 0 & 1 \\ 1 & 1 \end{bmatrix}, \quad Q_2 = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$$

(2.8.1)

Since the KRM expansions involve the fixed polarity expansions, then,  $e_i$  coefficients should contain  $c_i$  coefficients. Thus,

$$Q_0 = W_0, \quad Q_1 = W_1 \tag{2.8.2}$$

Like the matrix W, the matrix Q can be expressed as

$$Q_m = Q_{m_{n-1}} * Q_{m_{n-2}} * \dots * Q_{m_0}$$

(2.8.3)

where  $Q_{m_i} = Q_0$ , or  $Q_1$ , or  $Q_2$ , depending on the base selected ( $\begin{bmatrix} 1 & x_i \end{bmatrix}$ , or  $\begin{bmatrix} 1 & \overline{x_i} \end{bmatrix}$ , or  $\begin{bmatrix} x_i & \overline{x_i} \end{bmatrix}$ ) for each variable, respectively. Thus, the transform from  $a_i$  coefficients to  $e_i$  coefficients is

$$E = Q_m \cdot A \tag{2.8.4}$$

In order to obtain  $e_i$  coefficients from  $b_i$  coefficients, the three basic matrixes are

$$K_{0} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}, \quad K_{1} = \begin{bmatrix} 1 & 1 \\ 0 & 1 \end{bmatrix}, \quad K_{2} = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}$$

(2.8.5)

Similarly to the matrix Q, the matrix K is expressed as

$$K_{m} = K_{m_{n-1}} * K_{m_{n-2}} * \dots * K_{m_{0}}$$

(2.8.6)

Clearly, the matrix K and the matrix Z should have the following relationships

$$K_0 = Z_0, \quad K_1 = Z_1 \tag{2.8.7}$$

Thus, the transform from  $b_i$  coefficients to  $e_i$  coefficients is

$$E = K_m \cdot B \tag{2.8.8}$$

#### 2.9 Inconsistent Forms

The  $3^n$  KRM expansions, which are generated in a systematic or consistent way, are not the only possible canonical expansions. In fact, if the polarity of each literal in the zero polarity RM expansion can be freely chosen, there exist  $2^{n2^{n-1}}$  possible RM canonical expansions[Davio 78, Green 91A, Sasao 93B]. This is because there are  $2^n$ terms for the *n* variable RM canonical expansion and the  $2^n$  terms contain  $n2^{n-1}$ literals. That is, in equation (2.3.7), any single literal *a* ( $\overline{a}$ ) can be substituted by  $\overline{a} \oplus 1$ ( $a \oplus 1$ ).

These  $2^{n2^{n-1}}$  possible RM canonical expansions have been termed inconsistent GRM forms[Green 91B]. In practice, this large set contains  $3^n$  consistent RM expansions, i.e. KRM expansions.

Furthermore, arbitrary products terms combined by XORs are called an Exclusive OR sum of products (ESOP) which is the most general AND-XOR expression. There are at most  $3^{tn}$  different ESOPs[Sasao 93B], where *t* is the number of the products.

#### 2.10 Dual Forms of RM Expansions

Dual forms of RM expansions are investigated by Green[Green 94]. He introduces an operation termed logical equivalence (LEQ). This operation is identical to XNOR operation in the Boolean domain. In the following, the basic operations are described. For easy comparison with operations (2.2.1)~(2.2.7) described above, the same number order is employed, and symbol " $\overline{\oplus}$ " is used for LEQ operation, i.e. XNOR operation.

1. Closure laws

$$a\overline{\oplus}b$$

also two-valued (2.10.1)

| 2. Associative laws  | $a\overline{\oplus}b\overline{\oplus}c = (a\overline{\oplus}b)\overline{\oplus}c = a\overline{\oplus}(b\overline{\oplus}c)$ | (2.10.2) |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|----------|

| 3. Distributive laws | $a \cdot (b \overline{\oplus} c) = a \cdot b \overline{\oplus} a \cdot c$                                                   | (2.10.3) |

| 4. Commutative laws  | $a\overline{\oplus}b = b\overline{\oplus}a$                                                                                 | (2.10.4) |

| 5. Identities        | $a\overline{\oplus} 1 = a$                                                                                                  | (2.10.5) |

| 6.                   | $a \overline{\oplus} a = 1$                                                                                                 | (2.10.6) |

| 7.                   | $a\overline{\oplus} 0 = \overline{a}$                                                                                       | (2.10.7) |

Similarly to (2.2.8) and (2.2.9)

$$a\overline{\oplus}b = \overline{a}\overline{\oplus}\overline{b} \tag{2.10.8}$$

$$\overline{a}\overline{\oplus}b = a\overline{\oplus}\,\overline{b} = \overline{a\overline{\oplus}b} \tag{2.10.9}$$

It is not difficult to find that equations (2.10.8) and (2.10.9) have similar properties to equations (2.2.8) and (2.2.9).

There are some relationships between XOR and XNOR operations, they are

\_\_\_\_\_

$$a\overline{\oplus}b = \overline{a \oplus b} = a \oplus b \oplus 1 \tag{2.10.10}$$

$$\overline{a} \overline{\oplus} \overline{b} \overline{\oplus} \overline{c} \overline{\oplus} \dots = \overline{a \oplus b \oplus c \oplus \dots}$$

(2.10.11)

$$a\overline{\oplus}b\overline{\oplus}c\overline{\oplus}\dots = \overline{a}\oplus\overline{b}\oplus\overline{c}\oplus\dots$$

(2.10.12)

In the Boolean domain, there exists another algebraic form to describe a truth table, this is the conjunctive canonical expansion, also called product of sum (POS) canonical expansion, which is based on maxterm  $M_i$ . It is

$$f(x_{n-1}, \dots, x_1, x_0) = \prod_{i=0}^{2^n - 1} (a_i + M_i) = (a_0 + M_0) \cdot (a_1 + M_1)$$

$$\dots \dots (a_{2^n - 1} + M_{2^n - 1})$$

(2.10.13)

where  $\prod$  represents logical product (AND operation).

Similarly to the conjunctive canonical expansion, in the RM domain, dual forms of RM expansions can be established.

Assume that the Kronecker matrix product operates with XNOR and OR, that is

$$\begin{bmatrix} a & b \end{bmatrix} \bullet \begin{bmatrix} c & d \end{bmatrix} = \begin{bmatrix} a+c & a+d & b+c & b+d \end{bmatrix}$$

(2.10.14)

Also, if  $\stackrel{\wedge}{B}$  is the dual form of *b* coefficients, i.e.

$$\overset{\wedge}{B} = \begin{bmatrix} \overset{\wedge}{b}_{2''-1} & \cdots & \overset{\wedge}{b}_{2} & \overset{\wedge}{b}_{1} & \overset{\wedge}{b}_{0} \end{bmatrix}$$

where  $\hat{b}_i \in \{0,1\}$ , termed  $\hat{b}_i$  coefficients. Therefore, a POS canonical expansion in the RM domain can be set up wherein the OR operation provides the "sum" and XNOR gives the "product". The basis vector is  $\begin{bmatrix} 0 & x_i \end{bmatrix}$ .

$$f(x_{n-1}, \dots, x_1, x_0) = \{ [0 \ x_{n-1}] \bullet \dots \bullet [0 \ x_2] \bullet [0 \ x_1] \bullet [0 \ x_0] \} \circ \stackrel{\wedge}{B}$$

(2.10.15)

where the operator " $\circ$ " represents matrix multiplication based on XNOR and OR. For example, if n=3

$$f(x_{2}, x_{1}, x_{0}) = \{ \begin{bmatrix} 0 & x_{2} \end{bmatrix} \bullet \begin{bmatrix} 0 & x_{1} \end{bmatrix} \bullet \begin{bmatrix} 0 & x_{0} \end{bmatrix} \} \circ \overset{\wedge}{B} \\ = \begin{bmatrix} 0 & x_{0} & x_{1} & x_{1} + x_{0} & x_{2} & x_{2} + x_{0} & x_{2} + x_{1} & x_{2} + x_{1} + x_{0} \end{bmatrix} \circ \overset{\wedge}{B} (2.10.16) \\ = \overset{\wedge}{b}_{7} \overline{\oplus} (\overset{\wedge}{b}_{6} + x_{0}) \overline{\oplus} (\overset{\wedge}{b}_{5} + x_{1}) \overline{\oplus} (\overset{\wedge}{b}_{4} + x_{1} + x_{0}) \overline{\oplus} (\overset{\wedge}{b}_{3} + x_{2}) \\ \overline{\oplus} (\overset{\wedge}{b}_{2} + x_{2} + x_{0}) \overline{\oplus} (\overset{\wedge}{b}_{1} + x_{2} + x_{1}) \overline{\oplus} (\overset{\wedge}{b}_{0} + x_{2} + x_{1} + x_{0}) \}$$

Similarly to the situations in ESOP form, the dual forms of the fixed polarity expansions can be deduced by using the extra basis vector  $\begin{bmatrix} 0 & \overline{x_i} \end{bmatrix}$  for some variables, and those for KRM expansions can be derived by employing the third basis vector  $\begin{bmatrix} \overline{x_i} & x_i \end{bmatrix}$ . In addition, the transforms of the dual coefficients can be established by using a similar matrix technique[Green 94].

#### 2.11 Map Method

The map method is an efficient and powerful means to deal with coefficient conversion and minimization for a logic function in the RM domain, it also forms a basis of many other algorithms. A RM coefficient map termed  $b_i$  coefficient map (simply called  $b_i$  map) was introduced by Wu et al[Wu 82]. The  $b_i$  map can be used to transform  $a_i$  coefficients to  $b_i$  coefficients and  $c_i$  coefficients, and also, it can be employed to minimize a RM expansion. The minimized result is in a mixed polarity RM representation. This map, refined by Tran[Tran 87], who generalized the  $b_i$  map to deal with incompletely specified functions. In addition, minimization of a RM expansion can be carried out, not only on RM coefficient maps, but also on Karnaugh maps, even on any of the transition maps[Tran 87, 89].

The  $b_i$  map, in format, is similar to the Karnaugh map (k map), but its entries do not represent the function output in the same manner as do the minterm entries plotted on a k map. For ease of comparison, a four variable k map and a four variable  $b_i$  map are shown together in Fig. 2.11.1

| x <sub>3</sub><br>x <sub>2</sub> | 00              | 01              | 11              | 10              | X <sub>1</sub><br>X <sub>2</sub><br>X <sub>2</sub> | ,<br>00         | 01   | 11              | 10              |

|----------------------------------|-----------------|-----------------|-----------------|-----------------|----------------------------------------------------|-----------------|------|-----------------|-----------------|

|                                  | ·····           |                 | · · ·           | 10              | X 2                                                | 00              | 01   |                 |                 |

| 00                               | a,              | a ,             | а,              | a <sub>2</sub>  | 00                                                 | b,              | b,   | <b>b</b> 3      | <b>b</b> 2      |

| 01                               | a₄              | a,              | a,              | a               | 01                                                 | b₄              | b₅   | b,              | b,              |

| 11                               | a <sub>12</sub> | a <sub>13</sub> | a <sub>15</sub> | a <sub>14</sub> | 11                                                 | b <sub>12</sub> | b 13 | b <sub>15</sub> | b 14            |

| 10                               | a,              | а,              | a <sub>11</sub> | a <sub>10</sub> | 10                                                 | b <sub>s</sub>  | b,   | b11             | b <sub>10</sub> |

(a). k map in the Boolean domain.

(b).  $b_i$  map in the RM domain.

Fig. 2.11.1. Maps for four variables.

It should be noted that the meaning of the subscript *i* in *k* map is different from that in  $b_i$  map. In *k* map, "0" means that a variable appears in its complemented form and "1" means that a variable appears in its true form. In  $b_i$  map, "0" means that a variable does not appear and "1" means that a variable appears in its true or complemented form, depending on the polarity[Green 86].

#### 2.11.1 Folding Technique

A folding technique[Wu 82, Besslich 83, Tran 87] can be employed to transform  $a_i$  coefficients to  $b_i$  coefficients and  $c_i$  coefficients. This can be used to find a fixed polarity expansion with the minimum "1" entries in the map. The procedures are as follows:

- (a). Construct the k map of a given logic function  $f(x_{n-1}, \dots, x_1, x_0)$ , where the number of variables are less or equal to six.

- (b). Decide the required polarity of fixed polarity RM expansion.

- (c). Select a particular variable  $x_i$ , fold  $\overline{x_i}$  over  $x_i$  and XOR the two portions. The resulting XOR values make up the portion  $x_i$  and the portion  $\overline{x_i}$  remains the same as that of the old map.

- (d). Repeat step (c) for all the other variables from the last map generated in (c).

An example is employed to show the folding technique. A four variable logic function is given in the Boolean domain

$$f(x_3, x_2, x_1, x_0) = \sum (2, 3, 5, 8, 10, 14)$$

(2.11.1)

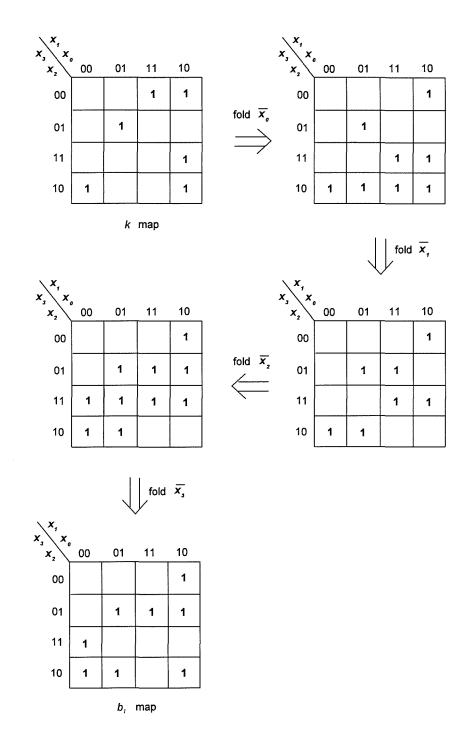

i.e.  $a_2 = a_3 = a_5 = a_8 = a_{10} = a_{14} = 1$ , transformation of  $a_i$  coefficients (Boolean) to  $b_i$  coefficients (zero polarity) is shown in Fig. 2.11.2

Fig. 2.11.2. An example to illustrate folding technique.

Note that the order of performing these individual folding operations does not affect the final result.

From the  $b_i$  map,  $b_2 = b_5 = b_6 = b_7 = b_8 = b_9 = b_{10} = b_{12} = 1$ . Hence

$f(x_3, x_2, x_1, x_0) = x_1 \oplus x_2 x_0 \oplus x_2 x_1 \oplus x_2 x_1 x_0 \oplus x_3 \oplus x_3 x_0 \oplus x_3 x_1 \oplus x_3 x_2 \quad (2.11.2)$

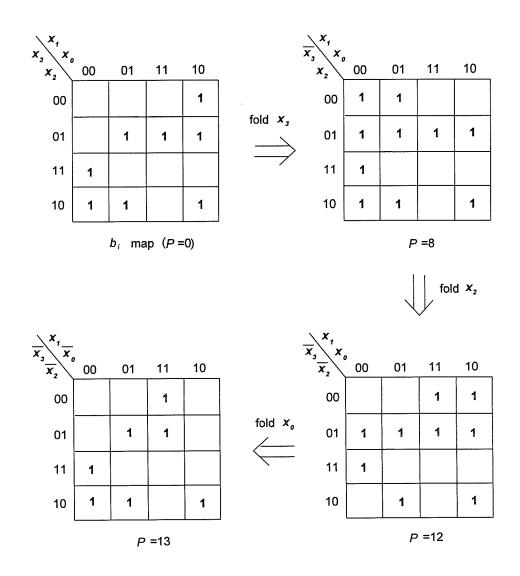

A similar folding technique can be employed to find any one of the  $2^{n} - 1$  fixed polarity RM expansions (not include P=0) from a  $b_{i}$  map. This is achieved by folding  $x_{i}$  over  $\overline{x_{i}}$ , instead of  $\overline{x_{i}}$  over  $x_{i}$ . For example, if polarity number  $P=13=(1101)_{2}$  is required for equation (2.11.2), this means that variables  $x_{3}$ ,  $x_{2}$  and  $x_{0}$  are required to convert to their complemented forms. This folding process is illustrated in Fig. 2.11.3. At the same time, the patterns for  $P=8=(1000)_{2}$  and  $P=(12)=(1100)_{2}$  are obtained.

Fig. 2.11.3. Folding for  $P = 13 = (1101)_2$ .

Thus, for P = 8

$$f(x_{3}, x_{2}, x_{1}, x_{0}) = 1 \oplus x_{0} \oplus x_{2} \oplus x_{2} x_{0} \oplus x_{2} x_{1} \oplus x_{2} x_{1} x_{0} \\ \oplus \overline{x_{3}} \oplus \overline{x_{3}} x_{0} \oplus \overline{x_{3}} x_{1} \oplus \overline{x_{3}} x_{2}$$

(2.11.3)

for P = 12

$$f(x_3, x_2, x_1, x_0) = x_1 \oplus x_1 x_0 \oplus \overline{x_2} \oplus \overline{x_2} x_0 \oplus \overline{x_2} x_1 \\ \oplus \overline{x_2} x_1 x_0 \oplus \overline{x_3} x_0 \oplus \overline{x_3} x_1 \oplus \overline{x_3} x_2$$

(2.11.4)

for P = 13

$$f(x_3, x_2, x_1, x_0) = x_1 \overline{x_0} \oplus \overline{x_2} \overline{x_0} \oplus \overline{x_2} x_1 \overline{x_0} \oplus \overline{x_3} \oplus \overline{x_3} \overline{x_0} \oplus \overline{x_3} x_1 \oplus \overline{x_3} \overline{x_2}$$

(2.11.5)

This can be checked by using  $\overline{x_i} \oplus 1$  to replace  $x_i$  step by step from equation (2.11.2) to equation (2.11.5).

As described above, it can be seen that a general procedure is: a k map is first converted to a  $b_i$  map for the polarity number P=0, and then, the  $b_i$  map is converted to a fixed polarity as required.

In practice, a coefficient set for a given fixed polarity can be obtained directly from a k map in n steps, which employs a tri-state map introduced by Tran[Tran 89]. A trimap is self-explanatory, its format is similar to that for k map.

In a tri-state, a variable has three states, true, complement and non-existent. Their respective labels in the maps are "1", "0" and "-". A variable in a tri-state map can exist in two of the three different states. The states of each variable can be readily found out by examining these labels. k maps with true and complement states are special cases in the tri-state maps. Polarisation is the process of converting a variable to a particular form, either true or complemented.

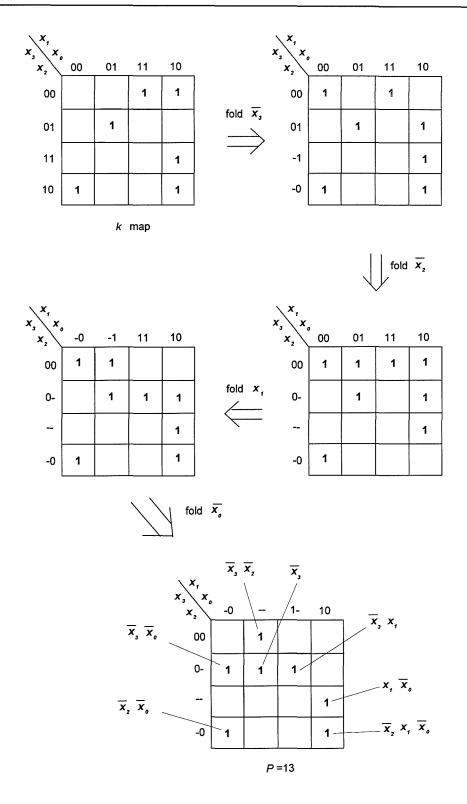

Polarisation for a given logic function starts from its k map, and the folding technique is used to polarize each variable, depending on the polarity required. A so called transition map is obtained every time a variable is polarized. The transition map obtained from the polarisation of the last variable is the RM coefficient map.

A tri-state map can be better understood by the illustration shown in Fig. 2.11.4, the same example as Fig. 2.11.2 is used. From the last map, it can be seen that, although the final result is the same as that in Fig. 2.11.3, the patterns for "1" entries in these two maps are different. In other words, different map formats have different explanations. There is a simple relationship between the two patterns. Assume that  $g_3g_2g_1g_0$  and  $h_3h_2h_1h_0$  in binary form are employed to represent the number of the cell in the two maps, then, the following relationship is set up

$\begin{array}{c}

g_3g_2g_1g_0\\

\oplus 1 \quad 1 \quad 0 \quad 1\\

h_3h_2h_1h_0

\end{array}$

P = 1101 is the polarity required. This can be readily generalized.

Fig. 2.11.4. A tri-state map to transform fixed polarity coefficients.

The folding technique can be readily extended to an incompletely specified function, in which, it includes some terms called don't care. Even though a don't care can be assumed to be an arbitrary value, "0" or "1", the result of a XOR operation for two don't care values does not have an arbitrary value but depends on those two don't care values that were assumed before the operation[Tran 87].

#### 2.11.2 Map Minimization

The  $b_i$  map can be employed to minimize a RM expansion, which is similar to the Karnaugh map. The major consideration is to obtain the minimum number of products for a given logic function in RM expansion, and the result can lead to a mixed polarity form.

Similarly to the Karnaugh map, the grouping is allowed for any group of  $2^n$  adjacent cells. A significant difference between  $b_i$  map and k map is that each "1" entry can be grouped only an odd number of times, and a "0" entry can also be grouped with "1" entries if it is grouped for an even number of times.

This minimisation procedure is

- (a). If a group is within the true domain of a variable  $\dot{x}_i$ , the true form  $\dot{x}_i$  appears in the product.

- (b). If a group is within the complemented domain of a variable  $\dot{x}_i$ , this variable does not appear in the product.

- (c). If a group spans both the true and complemented domains of a variable  $\dot{x}_i$ , the  $\frac{1}{x_i}$  complemented form  $\dot{x}_i$  appears in the product.

Where  $\dot{x}_i$  is  $x_i$  or  $\overline{x_i}$ .

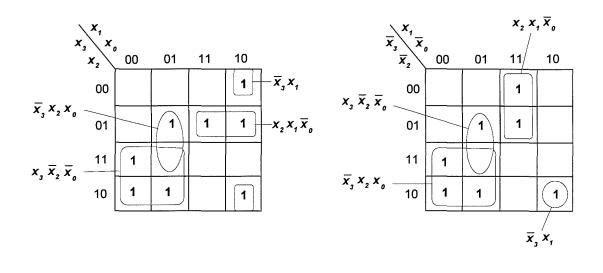

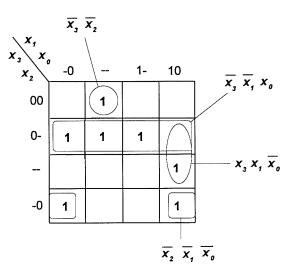

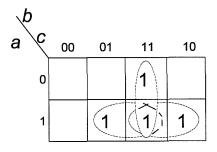

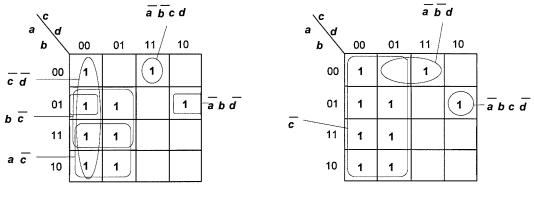

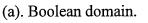

Two patterns of Fig. 2.11.3 are used to illustrate the minimization in Fig. 2.11.5

(a).  $P = 0 = (0000)_2$ . (b).  $P = 13 = (1101)_2$ .

Fig. 2.11.5. Two examples to illustrate map minimization.

From the map (a)

$$f(x_3, x_2, x_1, x_0) = \overline{x_3} x_2 x_0 \oplus x_3 \overline{x_2} \overline{x_0} \oplus x_2 x_1 \overline{x_0} \oplus \overline{x_3} x_1$$

(2.11.6)

From the map (b)

$$f(x_3, x_2, x_1, x_0) = x_3 \overline{x_2} \overline{x_0} \oplus \overline{x_3} x_2 x_0 \oplus x_2 x_1 \overline{x_0} \oplus \overline{x_3} x_1$$

(2.11.7)

It should be noted that the true forms of variables  $x_3$ ,  $x_2$ ,  $x_1$  and  $x_0$  in the map (b) are explained with  $\overline{x_3}$ ,  $\overline{x_2}$ ,  $x_1$  and  $\overline{x_0}$ , respectively, because of the polarity number P = 1101. Equations (2.11.6) and (2.11.7) can be easily checked from equations (2.11.2) and (2.11.5).

When minimization is carried out in a tri-state map, the minimization procedure stated previously should be modified to cover a non-existent state "-". Thus, the minimization procedure is:

- (a). If a group is within the true domain of a variable  $x_i$ , the true form  $x_i$  appears in the product.

- (b). If a group is within the complemented domain of a variable  $x_i$ , the complemented form  $\overline{x_i}$  appears in the product.

- (c). If a group spans both the true and complemented domains of a variable  $x_i$ , the complemented form  $\overline{x_i}$  appears in the product.

- (d). If a group spans both the true and non-existent domains of a variable  $x_i$ , the complemented form  $\overline{x_i}$  appears in the product.

- (e). If a group spans both the complemented and non-existent domains of a variable  $x_i$ , the true form  $x_i$  appears in the product.

This minimization procedure covers the cases not only for a tri-state map, but also for a transition map. In the following, an example for a tri-state map is given, see Fig. 2.11.6. This map is the last map in Fig. 2.11.4

Fig. 2.11.6. A minimization example in a tri-state.

From Fig. 2.11.6

$$f(x_3, x_2, x_1, x_0) = \overline{x_3} \, \overline{x_2} \oplus \overline{x_3} \, \overline{x_1} x_0 \oplus x_3 x_1 \, \overline{x_0} \oplus \overline{x_2} \, \overline{x_1} \, \overline{x_0}$$

(2.11.8)

A RM function can be minimized in a k map. According to equation (2.2.12), if two terms are mutually exclusive, inclusive OR (+) can be replaced by exclusive OR ( $\oplus$ ). Therefore, equation (2.3.1) can be rewritten as follows

$$f(x_{n-1}, \dots, x_1, x_0) = \sum_{i=0}^{2^n - 1} a_i m_i = a_0 m_0 \oplus a_1 m_1 \oplus \dots \oplus a_{2^n - 1} m_{2^n - 1}$$

(2.11.9)

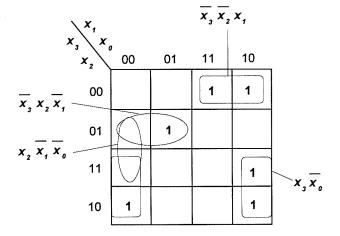

Equation (2.11.9) reveals that XOR operation can be a connective between all adjacent cells in a k map. This means that, for a given logic function, a k map can be employed to minimize its ESOP form or SOP form. The k map also directly generates a mixed form that contains both inclusive OR (+) and exclusive OR ( $\oplus$ ) in a two level representation. Fig. 2.11.7 shows an example for minimizing a logic function in ESOP in a k map.

Fig. 2.11.7. Using k map to minimize a logic function in ESOP.

From Fig. 2.11.7

$$f(x_3, x_2, x_1, x_0) = \overline{x_3} x_2 \, \overline{x_1} \oplus x_2 \, \overline{x_1} \overline{x_0} \oplus x_3 \, \overline{x_0} \oplus \overline{x_3} \, \overline{x_2} x_1$$

(2.11.10)

Equation (2.11.10) can be also written as

$$f(x_3, x_2, x_1, x_0) = (\overline{x_3} x_2 \,\overline{x_1} \oplus x_2 \,\overline{x_1} \,\overline{x_0} \oplus x_3 \,\overline{x_0}) + \overline{x_3} \,\overline{x_2} x_1 \tag{2.11.11}$$

This is because the term  $\overline{x_3} \, \overline{x_2} x_1$  circled conforms not only to RM rules, but also to Boolean rules.

As a k map can be used to minimize a logic function in the RM domain, the other maps may seem to be perplexing. When the "1" entries are lumped together or there are few "1" entries in a k map, a minimal expansion may be easily obtained directly from the k map. For a logic function with a high content of XOR operation, the "1" entries may be scattered in the k map, and patterns of XOR operation are not easily recognized, especially because "0" entries can be circled with "1" entries. Tran shows an example for this[Tran 89].

#### 2.12 Tabular Method

Although the map method does provide a powerful and compact means of representation for the display and manipulation of logic functions, it has its practical limitations. In general, the maps can only handle logic functions of six or less variables. In order to overcome this problem, similar to the Quine-McCluskey method in the Boolean domain, a tabular technique for RM logic was introduced by Almaini et al[Almaini 91, 94]. The tabular technique can convert  $a_i$  coefficients to  $b_i$  coefficients and  $c_i$  coefficients, and it can be used manually or programmed on a computer. In theory, it can be used for any number of variables. The technique is illustrated by means of an example. Assume that a logic function in the Boolean domain is

$$f(x_2, x_1, x_0) = \sum (0, 2, 3, 5)$$

(2.12.1)

(a). List all the minterms in binary form.

- (b). Select any variable  $x_i$ . For every term containing a "0" in position  $i(\overline{x_i})$ , generate an additional term with a "1" in position  $i(x_i)$ .

- (c). Compare newly generated entries with the ones that already exist cancelling pairs whenever they occur since  $\dot{x_i} \oplus \dot{x_i} = 0$ .

- (*d*). Repeat (*b*) and (*c*) for all other variables. The resulting uncancelled terms are the RM product terms in zero polarity.

| Minterms          | Terms generated by $x_2$ |

|-------------------|--------------------------|

| $x_{2}x_{1}x_{0}$ |                          |

| 0 0 0             | 1 0 0                    |

| 0 1 0             | 1 1 0                    |

| 0 1 1             | 1 1 1                    |

| 1 0 1             |                          |

| Terms | generated | by | $x_1$ |

|-------|-----------|----|-------|

|-------|-----------|----|-------|

| <i>x</i> <sub>2</sub> | $x_1$ | $x_0$      |  |   |   |            |

|-----------------------|-------|------------|--|---|---|------------|

| 0                     | 0     | 0          |  | 0 | 1 | $0 \times$ |

| 0                     | 1     | $0 \times$ |  | 1 | 1 | $1 \times$ |

| 0                     | 1     | 1          |  | 1 | 1 | $0 \times$ |

| 1                     | 0     | 0          |  |   |   |            |

| 1                     | 0     | 1          |  |   |   |            |

| 1                     | 1     | $0 \times$ |  |   |   |            |

| 1                     | 1     | $1 \times$ |  |   |   |            |

|                       |       |            |  |   |   |            |

|      | Terms generated by $x_0$ | • |

|------|--------------------------|---|

| 0 0  | 0 0 1                    |   |

| 1 1  | 1 0 1×                   |   |

| 0 1× |                          |   |

| 0 0  |                          |   |

From the remaining terms, the RM expansion is

$$f(x_2, x_1, x_0) = 1 \oplus x_0 \oplus x_1 x_0 \oplus x_2$$

(2.12.2)

The procedure can be reversed to convert  $b_i$  coefficients back to  $a_i$  coefficients. The tabular method has been developed to deal with don't care conditions[McKenzie 93]. It can be seen that the basic principle of the tabular technique is similar to that of the map folding technique. Therefore, the tabular technique can be developed to deal with such situations, in which, any  $c_i$  coefficients are transformed from the  $b_i$  coefficients, any  $c_i$  coefficients are found directly from  $a_i$  coefficients in n+1 steps for any n variable function[Almaini 91], and so on.

In addition, like the Quine-McCluskey method in the Boolean domain, the tabular technique can be readily developed for minimizing a RM function according to the rules in the RM domain[Helliwell 88, Green 93].

#### 2.13 Summary

This chapter introduced the background theory of RM logic that underlies many algorithms of RM logic in aspects of coefficients conversion, manipulation and minimization. There are a great deal of RM canonical expansions for a given logic function, and there is no known method for predicting the best polarity except for exhaustive search[Wu 82]. This makes it more complex for the manipulation and minimization in the RM domain than that in the Boolean domain. Sometimes, it may be difficult to decide the minimum expansion of a logic function unless all the canonical expansions of this function have been considered.

The map method in the RM domain is an efficient tool not only for minimizing a logic function, but also for transforming between RM coefficients and Boolean coefficients. The maps described in this chapter are the most commonly used maps in the RM domain, but not the only ones. For example, a so called ternary map[Green 90] has different format, which can be used to deal with the KRM Expansions. A ternary map, in principle, is similar to the maps discussed in this chapter. Like a Karnaugh map, a map in the RM domain is restricted to handle a logic function of not more six variables.

A tabular method, similar to the Quine-McCluskey method in the Boolean domain, can be employed to resolve this problem. In practice, in order to treat logic functions with more variables, near minimal solutions, namely heuristic algorithms, are employed instead of absolutely minimum algorithms[Sasao 93A]. Owing to the

complexity of exclusive-ORing "1" terms with "0" terms in minimization, no single method can guarantee a global minimum[Tran 93A].

RM expansions usually are two-level logic representations. Based on similar logic algebraic principle in the Boolean domain, it is not difficult to develop them in a multi-level structure[Saul 91]. For multi-output functions, algorithm strategies in the Boolean domain may be adopted to the RM domain[Lin 93, Saul 93, Sasao 93A].

# Chapter 3

# CMOS Implementation of Logic Circuits

#### **3.1 Introduction**

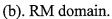

In the earlier days of logic design, a logic function was implemented by only using discrete components, such as INV, NAND, NOR, AND, OR, XOR and XNOR gates. Therefore, counting the number of gates used was often employed to estimate a hardware implementation cost. With the advance of integrated circuit (IC) technology, some complex gates, such as AOI (AND-OR-INV), OAI (OR-AND-INV), or even a single complex gate constructed of a series and a parallel circuit, can be used to realize a logic function. This is specially true in MOS circuit technology[Wu 85]. It is well known that a circuit implemented by complex gates is often more compact and faster, when compared to a logic function realized by individual gates.

The representation and minimization of logic functions, sometimes considered to be technology-independent, are in practical applications technology-dependent. For example, the implementation based on NAND gates for a given logic function is preferred in TTL technology, and the implementation based on NOR gates is better than other gates in NMOS technology. Therefore, a minimized SOP form for a logic function is often changed into NAND-NAND form for TTL circuit, and NOR-NOR form for NMOS circuit. This can be readily achieved by employing De Morgan's theorem.

For a given circuit technology or circuit style, an efficient method of logic design is required not only to concisely represent a logic function and easily minimize the function, but also to allow a simpler hardware realization.

CMOS technology offers many advantages over other IC technologies due to its high speed, high component density, low power requirement and low cost. It is thus dominant in digital circuits[Wu 87, Hurst 92, Weste 93]. Therefore, this work is concerned mainly with CMOS circuits.

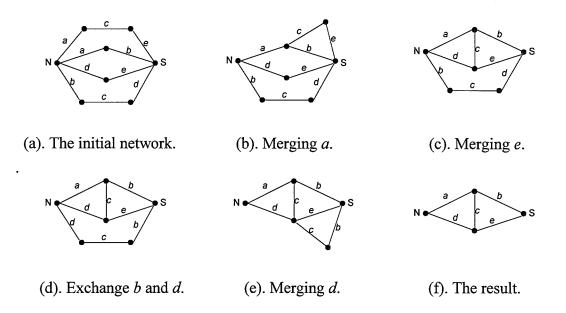

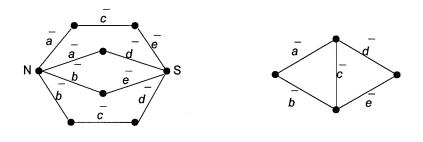

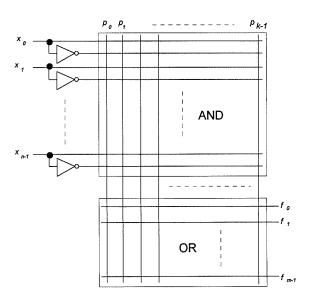

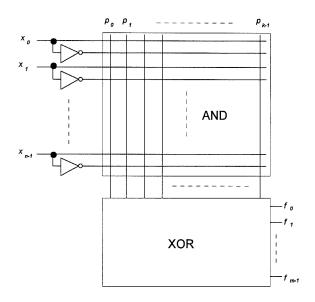

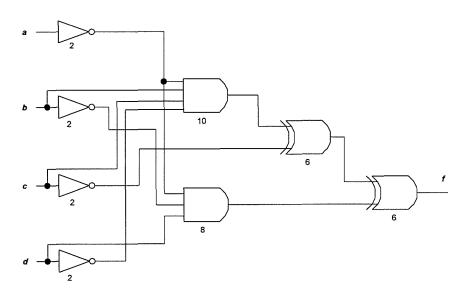

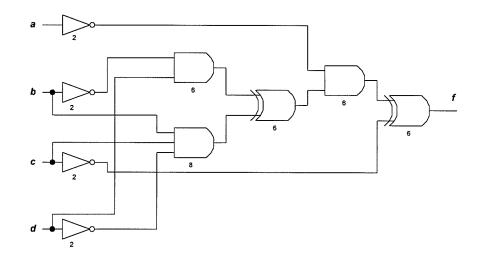

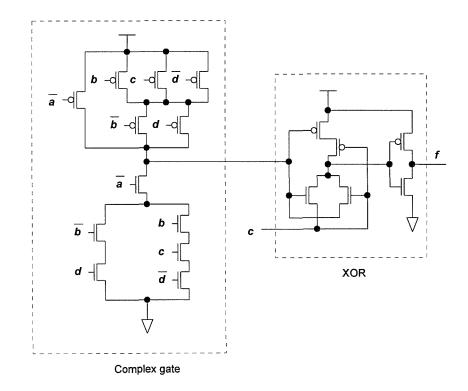

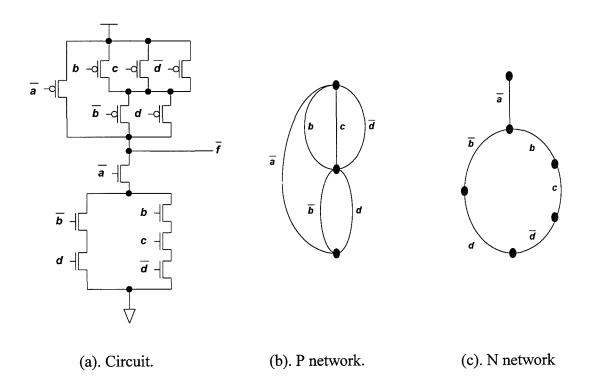

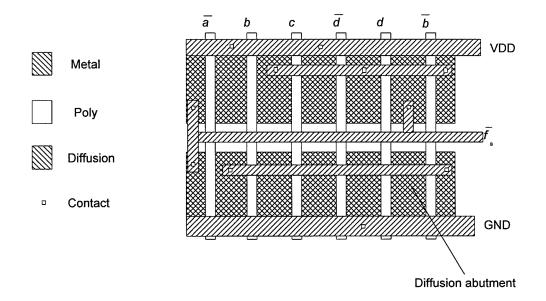

In this chapter, basic CMOS circuits are first described, then *switching network theory*, which was derived from the earlier Boolean logic design and now is a powerful tool in MOS circuit design[Wu 85], is reviewed. The circuit implementations based on Boolean logic and RM logic are investigated and compared. This investigation is related to gate level design, transistor level design and layout level design, but the comparison at the transistor level is emphasized. The implementations in PLA and FPGA, which are often considered to favor RM logic[Sasao 90, Csanky 93], are also studied. The mixed representations based on RM logic are introduced to minimize the implementation for RM logic. The main results about testing RM circuits are reviewed.

# **3.2 CMOS Circuits**

CMOS circuits may be divided into two categories, dynamic circuits and static circuits, according to whether they require a clock, or not. Dynamic CMOS circuits and static CMOS circuits can be further divided into different circuit styles, which may be suitable for different applications. Weste and Eshraghian describe their advantages and disadvantages[Weste 93].

The complementary CMOS circuit (also called the true CMOS circuit) is a typical static circuit, and also, its design theory underlies other circuit styles. In applications, the complementary CMOS circuit is one of the most commonly used circuit styles, it is widely employed to construct standard cells in the gate library of a CAD suite, gate array, functional cells, and so on[Hurst 92, Weste 93], because it is reliable and simple for design. All complementary gates may be designed as ratioless circuits. That is, if all transistors are the same size the circuit will function correctly (compared to some other MOS logic families where this is not the case)[Weste 93]. Therefore, this section is concerned mainly with this circuit style.

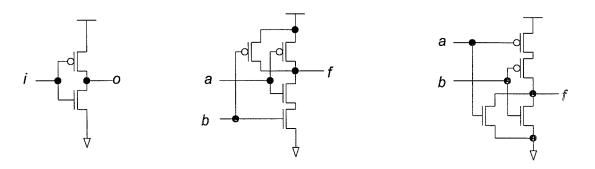

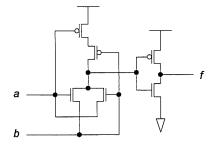

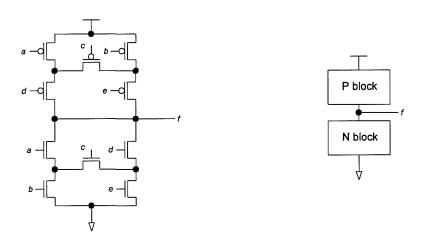

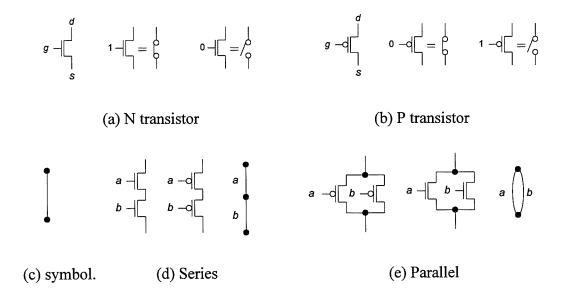

(a). Inverter.

(b). 2 input NAND gate.

(c). 2 input NOR gate.

Fig. 3.2.1. Three basic CMOS circuits.

In the complementary CMOS circuit, the minimum basic gates are composed of three gates, INV, NAND and NOR, which are shown in Fig. 3.2.1. The so-called minimum basic gates, here, mean that these three gates can't be decomposed further, and also, any kind of gates can be constructed by only using these three basic gates. An AND (OR) gate is constructed by a NAND (NOR) gate with an INV. According to the series and parallel principle, (N)AND gate and (N)OR gate can be easily extended for multi-input gates, but in practice, the number of inputs is restricted to four if high-speed circuits are desirable.

Since electrons have a higher mobility than holes, N type transistors are inherently faster by a factor of about 2.5 than P type transistors. Therefore, the NAND gate is better than the NOR gate in respect to speed, because of the slower P type transistors in parallel and faster N transistors in series for a NAND gate.

XOR and XNOR gates are often classified as complex gates. The reason for this is that, firstly, a single two input X(N)OR gate is usually more complex to realize than a single two input (N)AND gate or (N)OR gate; secondly, unlike (N)AND and (N)OR gates, X(N)OR gates can't be extended for the multi-input gates by simply employing the series or parallel principle. Therefore, in many situations, a multi-input X(N)OR gate is constructed by several two input gates. This problem also occurs in many other circuit technologies.

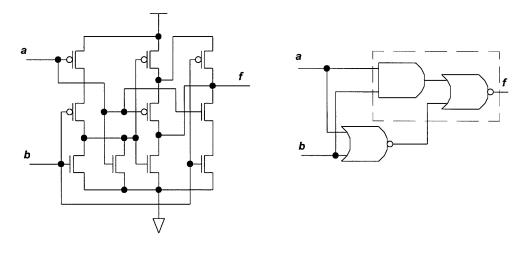

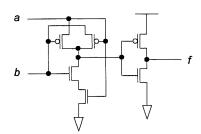

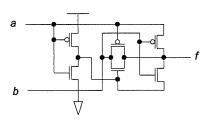

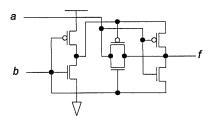

(a). Transistor form.

(b). Gate form.

Fig. 3.2.2. Complementary CMOS XOR gate.

(a). XOR gate with buffer output.

(c). XNOR gate with buffer output.

(b). XOR gate without buffer output.

(d). XNOR gate without buffer output.

Fig. 3.2.3. Pass transistor XOR and XNOR gates.

The simplest two input XOR gate known in complementary CMOS requires ten transistors, it is shown in Fig. 3.2.2. In many practical applications, two kinds of X(N)OR gates with pass transistors are widely employed, which are shown in Fig.

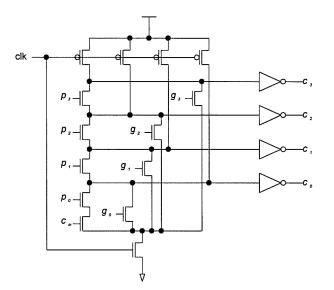

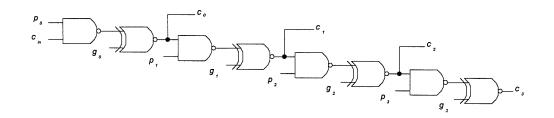

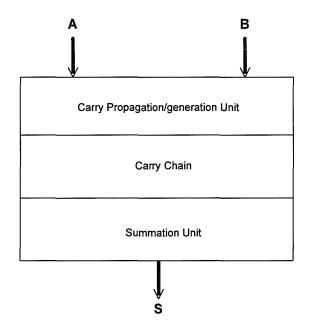

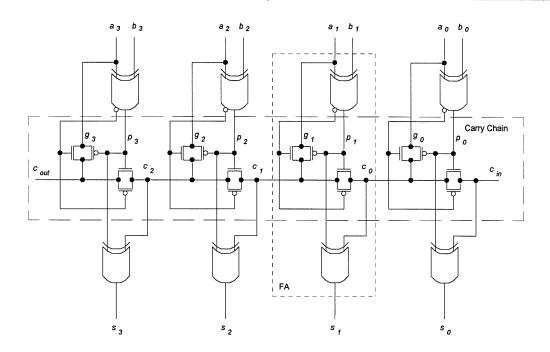

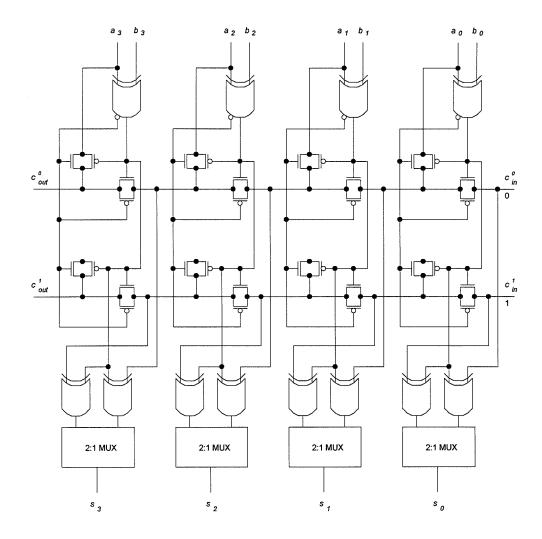

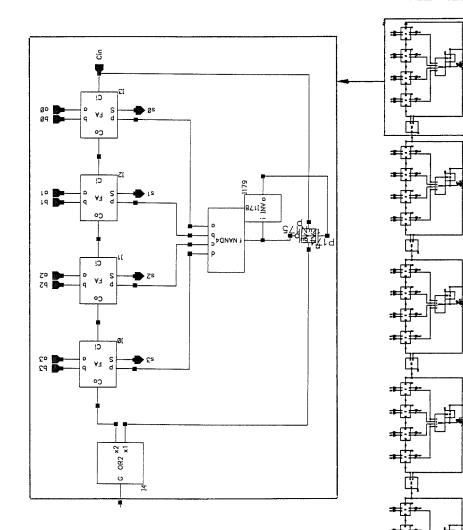

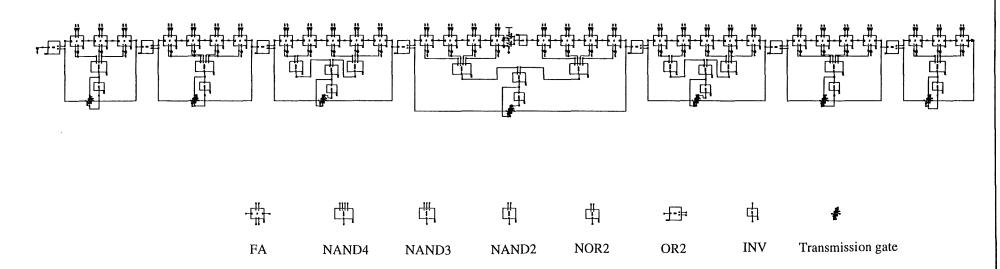

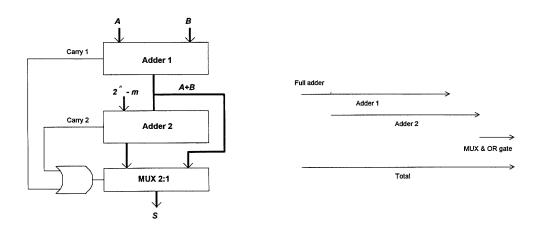

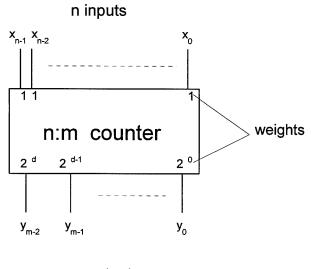

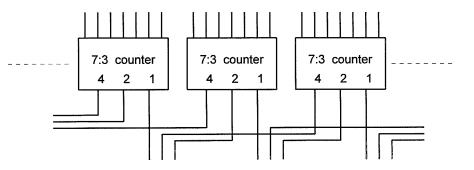

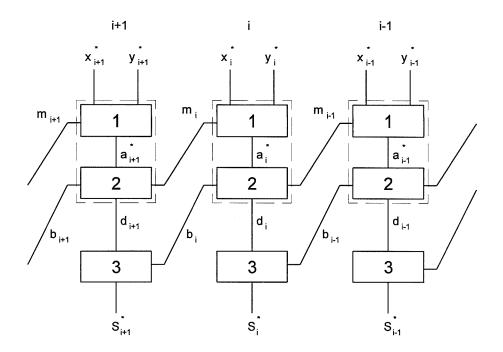

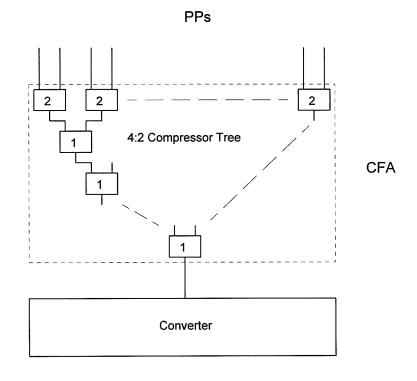

3.2.3. If both true and complemented forms of each variable are available, this is called double rail logic, less transistors can be used to construct an X(N)OR gate[Weste 93]. In the following, it is assumed that single rail logic is available, i.e., only the true form for each variable is available as a primary input unless otherwise stated.